Name:\_\_\_\_\_

### **COVER SHEET:**

Final Exam – Fall Semester 2005

Name:\_\_

#### Remember to show <u>ALL</u> work here and in <u>EVERY</u> problem on this exam.

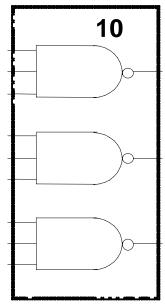

(10 pts.)

Draw a mixed-logic circuit diagram (with the minimum number of gates) to <u>directly implement</u> the below equation. All inputs and the output can be of any activation-level desired. Be sure to **specify** the desired activation levels. Do <u>not</u> simplify this equation. You may only use gates available on 74HC10 chips (shown). Use as many 74HC10 chips as you need, but use the minimum number required to solve this problem.

$A\overline{E} (\overline{B} + C) D = Y$

Final Exam – Fall Semester 2005

Name:\_\_\_

**2.** Answer the following for the given next-state <u>truth (logic) table</u>. Y and Z are outputs and X is the only input.

(14 pts.)

| Х | Q | $2 Q_1$ | <b>Q</b> <sub>0</sub> | Y | Ζ | $Q_2^+$ | $Q_1^+$ | $Q_0^+$ |

|---|---|---------|-----------------------|---|---|---------|---------|---------|

| 0 | 0 | 0       | 0                     | 0 | 0 | 1       | 1       | 1       |

| 0 | 0 | 0       | 1                     | 0 | 0 | 0       | 0       | 0       |

| 0 | 0 | 1       | 0                     | 0 | 0 | 0       | 0       | 1       |

| 0 | 0 | 1       | 1                     | 1 | 1 | 0       | 1       | 0       |

| 0 | 1 | 0       | 0                     | Х | Х | Х       | Х       | Х       |

| 0 | 1 | 0       | 1                     | Х | Х | Х       | Х       | Х       |

| 0 | 1 | 1       | 0                     | 1 | 0 | 0       | 1       | 1       |

| 0 | 1 | 1       | 1                     | 1 | 1 | 1       | 1       | 0       |

| 1 | 0 | 0       | 0                     | 0 | 0 | 1       | 1       | 1       |

| 1 | 0 | 0       | 1                     | 0 | 0 | 1       | 1       | 1       |

| 1 | 0 | 1       | 0                     | 0 | 0 | 1       | 1       | 1       |

| 1 | 0 | 1       | 1                     | 1 | 0 | 1       | 1       | 1       |

| 1 | 1 | 0       | 0                     | Х | Х | 1       | 1       | 1       |

| 1 | 1 | 0       | 1                     | Х | Х | 1       | 1       | 1       |

| 1 | 1 | 1       | 0                     | 1 | 0 | 1       | 1       | 1       |

| 1 | 1 | 1       | 1                     | 1 | 0 | 1       | 1       | 1       |

a) What **kind** of output is Y; and what **type** is Z? Be specific.

Y: (1 pt.)

Z: (1 pt.)

Final Exam – Fall Semester 2005

Name:\_\_\_\_\_

#### 2. (continue)

Design a circuit to implement the truth table from the previous page.

- Use only a <u>ROM</u> and D-FF's. Use <u>no</u> other SSI, MSI or LSI elements.

- The signals X and Y are active-high and Z is active-low.

- Use as little of the EEPROM as possible. List the ROM contents in order stating at address 0

- (b) Complete the following circuit by drawing in the appropriate number of D-FF's and show connections to <u>all</u> EEPROM signals. (4 pts.)

|   | EEPROM |     |  |  |  |  |

|---|--------|-----|--|--|--|--|

|   |        | Vcc |  |  |  |  |

|   | A7     | GND |  |  |  |  |

|   | A6     |     |  |  |  |  |

|   | A5     | D7  |  |  |  |  |

|   | A4     | D6  |  |  |  |  |

|   | A3     | D5  |  |  |  |  |

|   | A2     | D4  |  |  |  |  |

|   | A1     | D3  |  |  |  |  |

|   | A0     | D2  |  |  |  |  |

|   |        | D1  |  |  |  |  |

| С | CE     | D0  |  |  |  |  |

(c) List the ROM contents in order stating at address 0, with both address and data specified <u>in HEX</u>. Program Zeros for "Don't Cares" (8 pts.)

Final Exam – Fall Semester 2005

Name:\_\_\_

# 3. Hand Assembly & Program Analysis (Use the G-CPU information in the appendix)

Assume that you are given an 8Kx8 EPROM that has been erased completely. i.e. all memory contents are now \$FF.

(14 pts.)

Hand Assemble the following G-CPU program and show the contents of EPROM memory (Address & Data) that has been modified after the EPROM is programmed:

| T1<br>T2<br>T3 | ORG<br>dc.b<br>dc.b<br>dc.b<br>ORG | \$0080<br>\$45<br>\$88<br>%10101101<br>\$0 |

|----------------|------------------------------------|--------------------------------------------|

|                | LDAA                               | \$81                                       |

|                | LDAB                               | T1                                         |

|                | OR_BA                              |                                            |

|                | LDX                                | #\$0180                                    |

| TOP            | STAA                               | \$12,X                                     |

|                | BN                                 | TOP                                        |

(a) EPROM Memory Programmed due to the above Data & G-CPU Code:

|     | Addr (Hex)                   | <u>Data (Hex)</u>        | <u>Addr (Hex)</u> | <u>Data (Hex)</u>   | Addr (Hex)     | <u>Data (Hex)</u> |

|-----|------------------------------|--------------------------|-------------------|---------------------|----------------|-------------------|

|     |                              |                          |                   |                     |                |                   |

|     |                              |                          |                   |                     |                |                   |

|     |                              |                          |                   |                     |                |                   |

|     |                              |                          |                   |                     |                |                   |

|     |                              |                          |                   |                     |                |                   |

|     |                              |                          |                   |                     |                |                   |

|     |                              |                          |                   |                     |                |                   |

|     | In the above instruction?    | program what is t        |                   |                     |                | STX T1"           |

|     | -                            |                          |                   |                     | Hex            |                   |

| (c) | What is the e                | ffective address a       | associated w      | rith the "LDX #\$0" | 180" instructi | on?               |

|     |                              |                          |                   |                     |                | Hex               |

| (d) | What is the e                | effective address a      | associated w      | vith the "STX \$12, | X" instruction | n?                |

|     |                              |                          |                   |                     |                | Hex               |

|     | What is the v<br>branch occu | alue of the A regi<br>r? | ster the first    | time "STX \$12,X'   | is executed    | ? Will the        |

|     | A Register C                 | contents =               |                   |                     | cur (circle or | ne)? T or         |

|     |                              |                          | 5                 |                     |                |                   |

F

Final Exam – Fall Semester 2005

Name:\_\_\_\_\_

# 4. Program Execution (Use the G-CPU information in the appendix)

Given the following program in EPROM memory, fill out the cycle table that follows:

| (18 pts.)           | <u>Addr</u> | <u>Data</u> |

|---------------------|-------------|-------------|

| <b>、</b> 1 <i>/</i> | 0           | 02          |

|                     | 1           | 35          |

|                     | 2           | 06          |

|                     | 3           | 0A          |

|                     | 4           | 00          |

### Using the the G-CPU Controller ASM & Block Diagram (Appendix A handouts), complete the cycle table below:

| Cycle# | <u>R/-</u><br><u>W</u> | <u>PC</u><br>(Hex) | MAR  | <u>A15:0</u><br>(Hex) | <u>Data</u><br>(Hex) | IR (Hex) | <u>A (Hex)</u> | AddrSel1:0 |

|--------|------------------------|--------------------|------|-----------------------|----------------------|----------|----------------|------------|

| 1      | 1                      | 0000               | XXXX | 0000                  | 02                   | XX       | XX             | 00         |

| 2      |                        |                    |      |                       |                      |          |                |            |

| 3      |                        |                    |      |                       |                      |          |                |            |

| 4      |                        |                    |      |                       |                      |          |                |            |

| 5      |                        |                    |      |                       |                      |          |                |            |

| 6      |                        |                    |      |                       |                      |          |                |            |

| 7      |                        |                    |      |                       |                      |          |                |            |

| 8      |                        |                    |      |                       |                      |          |                |            |

| 9      |                        |                    |      |                       |                      |          |                |            |

| 10     |                        |                    |      |                       |                      |          |                |            |

Final Exam – Fall Semester 2005

Name:\_

### 5. Memory Maps, Memory Devices & Decoding

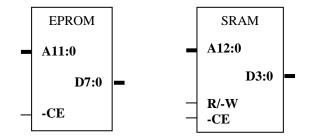

You are given as many of the following EPROM and SRAM devices that you need for the problem below:

(15 pts.)

If the processor is a GCPU with a 16 bit address bus (A15:0) and 8 bit data bus (D7:0), show the required **devices & decode circuitry** below to place an 8Kx8 EPROM starting <u>at 2000</u> <u>Hex</u> and an 8Kx8 SRAM immediately following the EPROM in the system memory map.

Implement the 8Kx8 EPROM. Show devices & connections (below) => Implement the 8Kx8 SRAM. Show devices & connections (below) =>

Show EPROM Memory Decode Circuit (below) => Show SRAM Decode Circuit (below) =>

Final Exam – Fall Semester 2005

Name:\_\_

## 6. GCPU Assembly Programming (Use the G-CPU instruction set in Appendix A)

(12 pts.)

Given the following constants in EPROM and SRAM Memory, write a program to fill the first **128 memory locations in SRAM with zeros**.

Assumptions:

- 1. EPROM exists in the memory map from 0-FFF Hex.

- 2. SRAM exists in the memory map from 1000-1FFF Hex.

- 3. Your program should begin at address 0 in EPROM.

- 4. Write a program to zero out (clear) the first 128 locations in SRAM.

Name:\_\_\_

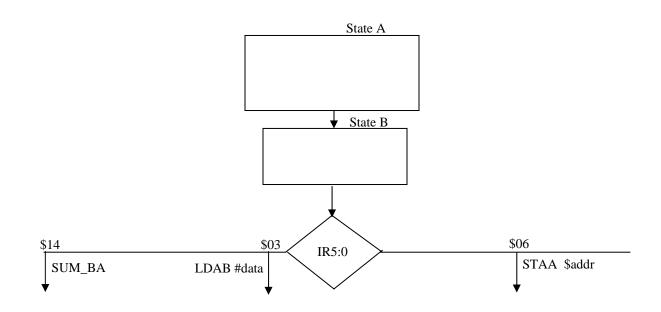

- 7. Controller (ASM) design for the G-CPU. (Use the G-CPU block diagram and ASM charts in the appendix.)

- (17 pts.)

Using the <u>signal names shown in controller</u> G-GPU block diagram in the appendix, complete the ASM chart (on the next page) to implement the following 3 instructions (**SUM\_BA, LDAB #data,** and **STAA \$addr**), including the <u>completion of State A and State B</u>.

#### Notes:

- (1) In each state and conditional output, specify only the signals that should be true.

- (2) However, you should use the notation: **MSA**=01, **MSB**=10, **MSC**=000.

- (3) When not specified, the default actions for each state is to "**hold**" **REGA and REGB** and **OUT = REGA.**

**Important Hint:** You should use the ASM charts provided in the appendix. Then, all you have to do is to determine what signals are supposed to be TRUE in each state.

| MSA1/MSB1 | MSA0/MSB0 |                 |

|-----------|-----------|-----------------|

| 0         | 0         | INPUT Bus       |

| 0         | 1         | REGA Output Bus |

| 1         | 0         | REGB Output Bus |

| 1         | 1         | OUTPUT Bus      |

|           |           |                 |

| <b>MSC2:0</b> (Most Significant Bit is on the left) |

|-----------------------------------------------------|

| 000 = > REGA Bus to OUTPUT Bus                      |

| 000 = > REGR Bus to OUTPUT Bus                      |

| 010 =  bit wise AND REGA/REGB Bus to                |

| OUTPUT Bus                                          |

| 011 =  bit wise OR REGA/REGB Bus to OUTPUT          |

| Bus                                                 |

| 100 = > complement of REGA Bus to OUTPUT Bus        |

| 101 =  REGA Bus Plus REGB Bus Plus Cin to           |

| OUTPUT Bus & Cout (There is an external             |

| Cin and an external Cout for the ALU)               |

| 110 =  shift REGA Bus left one bit to OUTPUT        |

| Bus (0 is shifted into OUTPUT Bus[0].)              |

| 111 =  shift REGA Bus right one bit to OUTPUT       |

| Bus (0 is shifted into OUTPUT Bus[3].)              |

|                                                     |

Put the solution on the next page.

Final Exam – Fall Semester 2005

Name:\_

8 (continued): Put solution here: