Name:\_\_\_\_\_

## COVER SHEET:

EEL 3701 – Digital Logic & Computer Systems Final Exam – Fall Semester 2006

Name:\_\_\_\_\_

### Remember to show <u>ALL</u> work here and in <u>EVERY</u> problem on this exam.

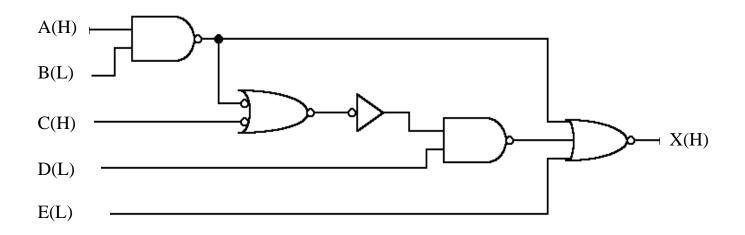

#### [10%] 1. Circuit Analysis

What is the logic equation for X in the given circuit? Do <u>not</u> simplify or transform it into an SOP or POS form. Leave the logic expression as it is after analysis. Also, draw the <u>intermediate</u> expression at the <u>input</u> to <u>each</u> gate.

- Notation reminder: A(H) is the same as A.H

- Boolean expression answers must be in lexical order, i.e., /A before A, A before B, etc.

EEL 3701 – Digital Logic & Computer Systems

Final Exam – Fall Semester 2006

Name:\_\_\_

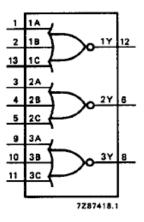

### [10%] 2. Circuit Synthesis

Draw a mixed-logic circuit diagram (with the minimum number of gates) to <u>directly implement</u> the below equation. All inputs and the output can be of any activation-level desired. Be sure to **specify the desired activation levels**. Do <u>not</u> simplify this equation. You may **only use** gates available on 74HC27 chips (shown). Use as many 74HC27 chips as you need, but use the minimum number required to solve this problem.

# F = A \* B \* C + C \* / D \* / E + A \* / B \* D

EEL 3701 – Digital Logic & Computer Systems Final Exam – Fall Semester 2006

Name:

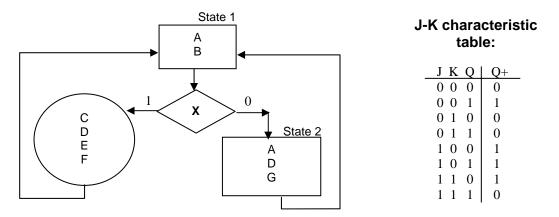

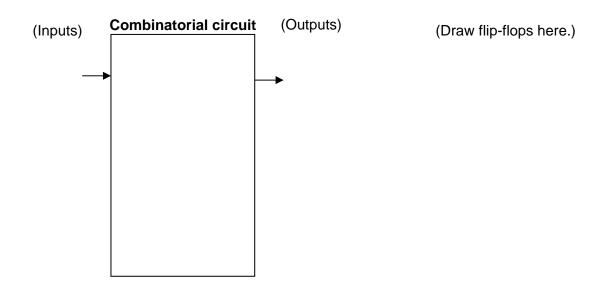

## [12%] 3. Implementation of an ASM chart using J-K flip-flops

- (a) Given the above ASM chart, complete the following block diagram of its implementation using the minimum number of J-K flip-flops: (2%)

- Determine how many J-K flip-flops that are needed.

- Draw in all the inputs and outputs of the combinatorial circuit.

- Make all necessary connections to complete the block diagram (between the combinatorial circuit and the flip-flops).

Name:\_

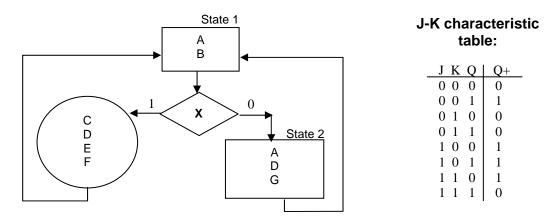

3. (continued) (ASM chart is repeated here for your convenience/)

(b) Finish the implementation of the ASM by determining the <u>minimum sum-of-products</u> (MSOP) logic expressions for the following signals: (10%)

| J | = |

|---|---|

| K | = |

| A | = |

| В | = |

| С | = |

| D | = |

| Ε | = |

| F | = |

G =

(If necessary, use the bottom/back of the previous page to do your work.)

Final Exam – Fall Semester 2006

1

Name:\_\_\_

| [12%] <b>4</b> . | Given th | e following | program | segment, | EQU | statements, | and | contents   | of m   | nemory |

|------------------|----------|-------------|---------|----------|-----|-------------|-----|------------|--------|--------|

|                  | location | S:          |         |          |     |             | Μ   | lemory Loc | ations | 3      |

|        | ORG            | 0           |   |       |     |        | Address | Content |

|--------|----------------|-------------|---|-------|-----|--------|---------|---------|

| 1      | LDX            | LDX #\$000C |   | Data0 | EQU | \$0026 | \$0026  | \$66    |

| 2      | LDAA           | #150;       |   | Datal | EQU | \$0032 | \$0032  | \$BB    |

| 3<br>4 | LDAB<br>SUM BA | #60;        |   | Data2 | EQU | \$0037 | \$0037  | \$74    |

| 4<br>5 | _              | nstructio   | m | Data3 | EQU | \$0038 | \$0038  | \$EC    |

| 5      | 110110 11      | d,e, or :   | / | Data4 | EQU | \$0050 | \$0050  | \$C3    |

|        |                |             | , | Data5 | EQU | \$00EF | \$00EF  | \$AB    |

|        |                |             |   | Data6 | EQU | \$5000 | \$5000  | \$3E    |

|        |                |             |   | Data7 | EQU | \$73AB | \$73AB  | \$AA    |

|        |                |             |   | Data8 | EQU | \$73AC | \$73AC  | \$E2    |

| a)     | Assume         | the         | 4 |       |     |        |         |         |

instructions in the above program segment have already been executed and the "next instruction" (i.e., 5th. instruction) is **LDAA 50**. Hand-assemble the LDAA instruction and fill in the blanks (including EA and register A) using <u>HEX</u>.

Note: EA is the "effective address", the actual <u>address in memory</u> where the data is loaded from in a "load" instruction (like LDAA, LDX, etc), or where the data is stored in a "store" instruction (like STAA). If no memory is accessed, write "none" for EA.

| ADDRESS | INSTRUCTION | HEX ADDRESS   | HEX VALUE |

|---------|-------------|---------------|-----------|

| \$0008  | LDAA 50     | \$0008        |           |

| EA =    |             | \$0009        |           |

| A =     |             | \$000A        |           |

|         |             | <u>\$000B</u> |           |

**Repeat the same problem** <u>if</u> the "next instruction" is the instruction in "b", "c", "d", "e", **or** "f", again assuming instructions 1 through 4 have been executed.

| b) | \$0008<br>EA =<br>X =                          |                      | <u>\$0008</u><br><u>\$0009</u><br><u>\$000A</u><br><u>\$000B</u>         |  |

|----|------------------------------------------------|----------------------|--------------------------------------------------------------------------|--|

| c) | EA =                                           | STAA 38,X<br><br>d = | _\$0008<br>_ <u>\$0009</u><br>_ <u>\$000A</u><br><u>\$000B</u>           |  |

| d) | \$0008<br>EA =<br>Y =                          |                      | _\$0008<br>_\$0009<br>_\$000A<br>_\$000B                                 |  |

| e) | \$0008<br>EA =<br>PC after this<br>instruction |                      | _ <u>\$0008</u><br>_ <u>\$0009</u><br>_ <u>\$000A</u><br>_ <u>\$000B</u> |  |

| f) | \$0008<br>EA =<br>PC after this<br>instruction |                      | _ <u>\$0008</u><br>_ <u>\$0009</u><br>_ <u>\$000A</u><br>\$000B          |  |

EEL 3701 – Digital Logic & Computer Systems Final Exam – Fall Semester 2006

Name:\_\_\_

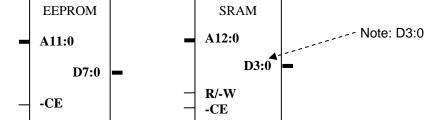

## [10%] 5. EEPROM and SRAM

You are given as many of the following EEPROM and SRAM devices that you need for the problem below:

You are to implement a 16Kx8 memory module, containing 8Kx8 SRAM, starting in location 0, followed immediately by 8Kx8 EEPROM.

The 16K X 8 memory module should have an "R/-W" input and a "-CE" input.

For ease of grading, draw the. 8Kx8 SRAM circuit here (i.e., show the devices & connections): Draw the 8Kx8 EEPROM circuit here (i.e., show the devices & connections):

EEL 3701 - Digital Logic & Computer Systems

Final Exam – Fall Semester 2006

Name:\_\_\_\_\_

[15%] 6. <u>Program Execution</u> (Use the G-CPU information in the back of the test.)

Given the following program in EPROM memory, fill out the following cycle table that illustrates its execution:

AddrData001107201307

Using the the <u>G-CPU Controller ASM</u> & Block Diagram (at the end of this test), complete the cycle table below. Use as many rows as you need.

| <u> </u> | <u>Cycle#</u> | <u>R/-</u><br><u>W</u> | <u>Addr</u><br><u>Sel1:0</u> | <u>PC</u><br>(Hex) | MAR  | <u>A15:0</u><br>(Hex) | <u>Data</u><br>(Hex) | <u>IR</u><br>(Hex) | <u>A</u><br>(Hex) | <u>B</u><br>(Hex) |

|----------|---------------|------------------------|------------------------------|--------------------|------|-----------------------|----------------------|--------------------|-------------------|-------------------|

|          | 1             | 1                      | 00                           | 0000               | 0400 |                       |                      | 06                 | 32                | 16                |

|          | 2             |                        |                              |                    |      |                       |                      |                    |                   |                   |

|          | 3             |                        |                              |                    |      |                       |                      |                    |                   |                   |

|          | 4             |                        |                              |                    |      |                       |                      |                    |                   |                   |

|          | 5             |                        |                              |                    |      |                       |                      |                    |                   |                   |

|          | 6             |                        |                              |                    |      |                       |                      |                    |                   |                   |

| $\Box$   | 7             |                        |                              |                    |      |                       |                      |                    |                   |                   |

|          | 8             |                        |                              |                    |      |                       |                      |                    |                   |                   |

|          | 9             |                        |                              |                    |      |                       |                      |                    |                   |                   |

|          | 10            |                        |                              |                    |      |                       |                      |                    |                   |                   |

EEL 3701 - Digital Logic & Computer Systems

Final Exam – Fall Semester 2006

Name:\_\_\_

## [15%] 7. <u>GCPU Assembly Programming</u> (Use the G-CPU instruction set in back of this test.)

Write an assembly language program using only the G-CPU instructions

- There are \$25 bytes already stored in memory starting in Location \$1000

- Your program should go through the \$25 bytes and count the number of "non-zero" bytes (i.e., bytes that are not equal to \$00).

- At the end of the program, Memory Location \$0FFF should contain the count of non-zero bytes.

- To increase your chances of partial credit, comment your program.

Important restriction: You have to use REGA as the "loop counter".

Name:\_

[16%] 8. <u>Controller (ASM) design for the G-CPU.</u> (Use the G-CPU block diagram and ASM charts in the back of the test.)

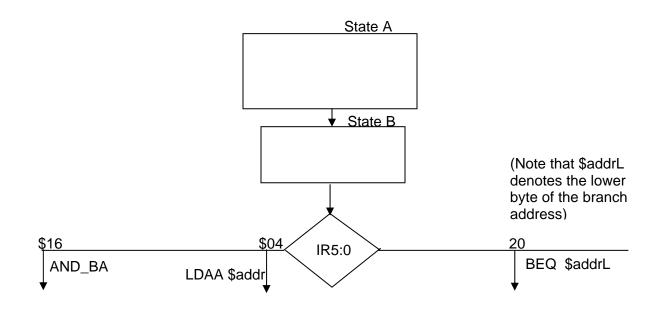

Using the <u>signal names shown in controller</u> G-GPU block diagram in the back of the test, complete the ASM chart (on the next page) to implement the following 3 instructions (**AND\_BA, LDAA \$addr,** and **BEQ \$addrL**), including the <u>completion of State A and State B</u>.

#### Notes:

- (1) In each state and conditional output, specify only the signals that should be true.

- (2) However, you should use the notation: MSA=01, MSB=10, MSC=000.

- (3) The default actions for each state should be specified to "**hold**" **REGA and REGB** and **OUT = REGA.**

- (4) For your convenience, the required values for MSA, MSB, and MSC are given below:

Table 1: Input source MUXs for Registers A and B.

| MSA1/<br>MSB1 | MSA0/<br>MSB0 | Bus Selected as Input<br>to REGA/REGB |

|---------------|---------------|---------------------------------------|

| 0             | 0             | INPUT Bus                             |

| 0             | 1             | REGA Bus                              |

| 1             | 0             | REGB Bus                              |

| 1             | 1             | OUTPUT Bus                            |

| MSC2:0 | Action                                     |

|--------|--------------------------------------------|

| 000    | REGA Bus to OUTPUT Bus                     |

| 001    | REGB Bus to OUTPUT Bus                     |

| 010    | complement of REGA Bus to OUTPUT Bus       |

| 011    | bit wise AND REGA/REGB Bus to OUTPUT Bus   |

| 100    | bit wise OR REGA/REGB Bus to OUTPUT Bus    |

| 101    | sum of REGA Bus & REGB Bus to OUTPUT Bus   |

| 110    | shift REGA Bus left one bit to OUTPUT Bus  |

|        | shift REGA Bus right one bit to OUTPUT Bus |

| 111    | without sign extension                     |

Table 2: ALU function selection MUX. (MUX C)

Put the solution on the next page.

EEL 3701 - Digital Logic & Computer Systems

Final Exam – Fall Semester 2006

Name:\_

## 8 (continued): Put solution here: