Name:\_\_\_\_\_

### **COVER SHEET:**

EEL 3701 – Digital Logic & Computer Systems Final Exam – Fall Semester 2007

Name:\_\_\_\_\_

### Remember to show <u>ALL</u> work here and in <u>EVERY</u> problem on this exam.

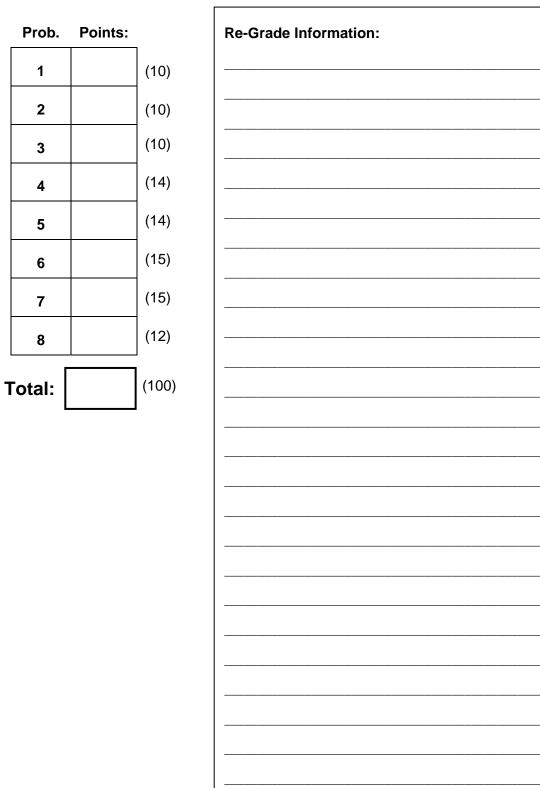

### [10%] 1. Circuit Analysis

What is the logic equation for X in the given circuit? Do <u>not</u> simplify or transform it into an SOP or POS form. Leave the logic expression as it is after analysis. Also, draw the <u>intermediate</u> expression at the <u>input</u> to <u>each</u> gate.

- Notation reminder: A(H) is the same as A.H

- Boolean expression answers must be in **lexical order**, i.e., /A before A, A before B, etc.

Final Exam – Fall Semester 2007

Name:\_\_\_

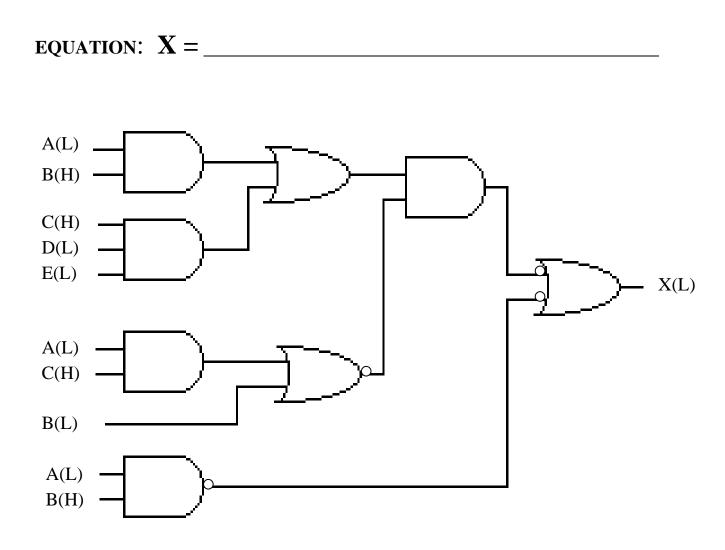

# [10%] 2. <u>Circuit Synthesis</u>

Draw a mixed-logic circuit diagram (with the minimum number of gates) to <u>directly implement</u> the below equation. All inputs and the output can be of any activation-level desired. Be sure to **specify the desired activation levels**. Do <u>not</u> simplify this equation. You may **only use** gates available on 74HC10 chips (shown). Use as many 74HC10 chips as you need, but use the minimum number required to solve this problem.

# $F = A^*B^*D + B^*/C^*/E + /A^*C^*/D$

EEL 3701 – Digital Logic & Computer Systems Final Exam – Fall Semester 2007

Name:

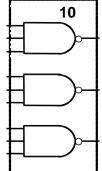

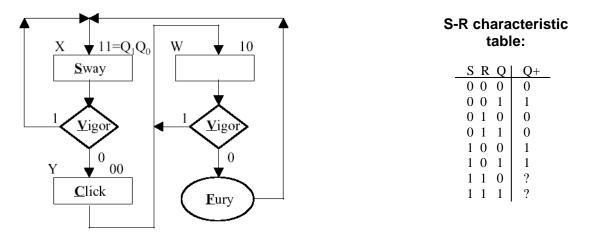

# [10%] 3. Implementation of an ASM chart using clocked S-R FFs

- (a) Given the above ASM chart, complete the following block diagram of its implementation using the minimum number of <u>clocked</u> S-R flip-flops: (2%)

- Determine how many clocked S-R flip-flops that are needed.

- Draw in all the inputs and outputs of the combinatorial circuit.

- Make all necessary connections to complete the block diagram (between the combinatorial circuit and the clocked S-R flip-flops).

Name:\_

**3. (continued)** (ASM chart is repeated here for your convenience)

(b) Finish the implementation of the ASM by determining the <u>minimum sum-of-products</u> (MSOP) logic expressions for all the output signals: (8%)

(If necessary, use the bottom/back of the previous page to do your work.)

Final Exam – Fall Semester 2007

Name:\_\_\_\_\_

[14%] 4. Assume the below has already been run, and the code that follows in a, b, c, d, e, f, g will follow. Hand assemble the following instructions and fill in the blanks. EA is the 16-bit effective address. If there is no effective address, write none. (Use the G-CPU instruction set attached to this test).

| Data0<br>Data1<br>Data2<br>Data3<br>Data4<br>Data5 | ORG<br>DC.B<br>ORG<br>DC.B<br>ORG<br>DC.B<br>ORG<br>DC.B<br>ORG<br>DC.B<br>ORG<br>DC.B | \$0032<br>\$66<br>\$0028<br>\$A3<br>\$002A<br>\$74<br>\$0038<br>\$EC<br>\$003A<br>\$EC<br>\$003A<br>\$EC<br>\$0040<br>\$AB | Data6<br>Data7<br>Data8 | ORG<br>DC.B<br>ORG<br>DC.B<br>ORG<br>LDX<br>LDAA<br>LDAB<br>SUM_AB | \$0048<br>\$3E<br>\$0058<br>\$9E<br>\$2A42<br>\$99, \$AC<br>\$0000<br>#\$000A<br>#3<br>#37 |

|----------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

|                                                    | INSTRUCI<br>STAB 48,                                                                   | TION                                                                                                                       | 00<br>00<br>00          | X ADDRESS<br>08<br>09<br>0A<br>0B                                  | HEX VALUE                                                                                  |

| b) \$0008<br>EA =<br>A =                           |                                                                                        |                                                                                                                            | _00                     | 08<br>09<br>0A<br>0B                                               |                                                                                            |

| c) \$0008<br>EA =<br>X =                           |                                                                                        | .a8                                                                                                                        | _ <u>00</u> _00         | 08<br>09<br>0A<br>0B                                               |                                                                                            |

| d) \$0008<br>EA =<br>A =                           |                                                                                        |                                                                                                                            | <u>00</u> 00            | 08<br>09<br>0A<br>0B                                               |                                                                                            |

| e) \$0008<br>EA =<br>B =                           | LDAB Dat                                                                               | .a8                                                                                                                        | <u>00</u> 00            | 08<br>09<br>0A<br>0B                                               |                                                                                            |

| f) \$0008<br>EA =<br>PC after<br>instr             |                                                                                        |                                                                                                                            | _ <u>00</u> 00          | 08<br>09<br>0A<br>0B                                               |                                                                                            |

| PC after                                           |                                                                                        |                                                                                                                            | _ <u>00</u> 00          | 08<br>09<br>0A<br>0B                                               |                                                                                            |

Final Exam – Fall Semester 2007

Name:\_\_

# [14%] 5. EEPROM and SRAM

Given as many 256x8 EEPROM chips and 256x8 static RAM chips as needed, design a 1024x8 memory module (with a CS) that has 512x8 of RAM at the lowest addresses and 512x8 of EEPROM at the highest addresses. The 512x8 of RAM must start at address 0 and the first address of the 512x8 of EEPROM must immediately follow the last RAM address. Add the minimum number of additional components required. Make sure the EEPROM is <u>NEVER</u> enabled during a write cycle and the RAM is enabled for <u>both</u> read and write cycles. The EEPROM and SRAM devices have active low CS and the SRAM devices have a R/W control signal.

- (2%) a) What is the address range for **each of the** memory components (in **binary** <u>and</u> in **hex**)?

- SRAM

EEPROM

(12%) b) Design the required memory device below. Make sure you show the memory module's inputs and outputs and all the individual memory component devices. Use labels instead of wires in the design.

Final Exam – Fall Semester 2007

Name:

[15%] **6. <u>HAND Assembly</u>** The following program finds all occurrences of \$37 in a table with an \$FF end of table marker and replaces them with \$AA. It uses the G-CPU instruction set attached to this test. Hand assemble the program in the space given.

| Address | Data<br>(Herr) | ] |       | Due en en      |                         |

|---------|----------------|---|-------|----------------|-------------------------|

| (Hex)   | (Hex)          | - |       | Program<br>ORG | \$100                   |

|         |                | - | Table | DC.B           | \$10,\$37,\$CC,\$37,\$1 |

|         |                |   | EOT   |                | \$FF                    |

|         |                |   | NEW   |                | \$AA                    |

|         |                | - | OLD   | EQU            | \$C8                    |

|         |                |   | OLD   | ORG            | \$200                   |

|         |                | - | STRT  |                | #Table                  |

|         |                |   |       | LDA            | EOT                     |

|         |                |   | LUUI  | COMB           | LUI                     |

|         |                |   |       | LDAA           | 0,X                     |

|         |                |   |       | SUM_BA         | 0,1                     |

|         |                | - |       | BEQ            | QUIT                    |

|         |                | - |       | LDAA           | 0,X                     |

|         |                | - |       | LDAA<br>LDAB   | #OLD                    |

|         |                | - |       | SUM_BA         | #OLD                    |

|         |                | - |       |                | NOCU                    |

|         |                |   |       | BNE            | NOSW                    |

|         |                | - |       | LDAA           | #NEW                    |

|         |                | - |       | STAA           | 0,X                     |

|         |                | - | NOSW  |                |                         |

|         |                | - |       | BNE            | LOOP                    |

|         |                | _ | QUIT  | BEQ            | QUIT                    |

|         |                |   |       |                |                         |

|         |                |   |       |                |                         |

|         |                |   |       |                |                         |

|         |                |   |       |                |                         |

|         |                | 1 |       |                |                         |

|         |                | 1 |       |                |                         |

|         |                | 1 |       |                |                         |

|         | 1              | 1 |       |                |                         |

|         |                |   |       |                |                         |

|         |                | - |       |                |                         |

|         |                | 4 |       |                |                         |

|         |                | - |       |                |                         |

|         |                | - |       |                |                         |

|         |                | 4 |       |                |                         |

|         |                | 4 |       |                |                         |

Final Exam – Fall Semester 2007

Name:\_\_\_

[15%] 7. <u>GCPU Assembly Programming</u> (Use the G-CPU instruction set attached to this test) Write an entire G-CPU program to copy all the positive values in a table called TAB1 (beginning at address \$3000) to another table called TAB2 (beginning at address \$7000). TAB1 has 200 1-byte values already in memory. There is a 16-KB ROM for your program, starting at address 0 and a 32-KB SRAM, starting at \$4000 for data. Be sure to initialize <u>all</u> necessary values, variables, etc., i.e., assume no initializations are done for you. Be sure to properly terminate the program (so it does not execute past the end of your program). Use labels instead of numbers in assembly instructions wherever possible.

| Labels | Instructions | Comments |

|--------|--------------|----------|

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

|        |              |          |

Final Exam – Fall Semester 2007

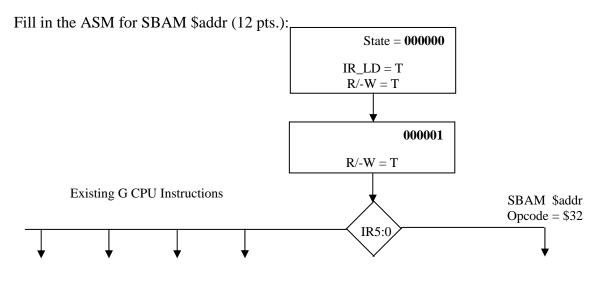

Name:\_

[12%] 8. <u>GCPU Instruction Design</u> (See the G-CPU Next State Table attached to this test) We want to implement a new instruction for the GCPU. The new instruction will be denoted as SBAM addr. It added the content of register B to register A (like SUM\_BA). But, it also stores the result into memory at location "addr". The new opcode for this instruction will be designated as \$32 and the next state available in the Controller's ASM is \$34. Show the additional states required to implement this new instruction in the Controller's ASM below and show all controller output signals that must be true in each new state for this new instruction:

# Assume: **R/-W** is True for **Read** and **F**alse for **Write**.

**Control Signals:** PC\_INC, PC\_LD\_Upper, PC\_LD\_Lower, MAR\_INC, MAR\_LD\_Upper, MAR\_LD\_Lower, X\_INC, X\_LD\_Upper, X\_LD\_Lower, Y\_INC, Y\_LD\_Upper, Y\_LD\_Lower, IR\_LD, R/-W, ADDR\_SEL1:0, XD\_LD, YD\_LD

Note1: The controller output signals are also shown in the G CPU Block Diagram for reference.

Final Exam - Fall Semester 2007

Name:\_

# **GCPU Instructions**

#### Data Movement Instructions:

| Data Movement |                  |      | nstr                  | uctions:                                         |                                                                  |                |             |                |  |  |  |

|---------------|------------------|------|-----------------------|--------------------------------------------------|------------------------------------------------------------------|----------------|-------------|----------------|--|--|--|

| Opcode        | Instruction      | ı    | Oper                  | and                                              | Description                                                      |                |             | # of<br>States |  |  |  |

| 0             | TAB              |      | none                  |                                                  | Transfer A to B (inherent addr<br>Transfer B to A (inherent addr |                |             | 2              |  |  |  |

| 1             | TBA              |      | none                  |                                                  |                                                                  | 2              |             |                |  |  |  |

| 2             | LDAA #dz         |      | 8 bit                 |                                                  | Load A with immediate data (i                                    | mmediate ad    | ldr.)       | 3              |  |  |  |

| 3             | LDAB #da         | ata  | 8 bit                 | data                                             | mmediate ad                                                      | ldr.)          | 3           |                |  |  |  |

| 4             | LDAA add         | ir   | 16 bi                 | t address                                        | Load A with data from memor<br>(extended addressing)             | y location ad  | ldr         | 5              |  |  |  |

| 5             | LDAB add         | łr   | 16 bi                 | t address                                        | Load B with data from memory<br>(extended addressing)            | y location ad  | cation addr |                |  |  |  |

| 6             | STAA add         | r    | 16 bi                 | t address                                        | Store data in A to memory loca<br>addressing)                    | ation addr (e: | xtended     | 5              |  |  |  |

| 7             | STAB add         | r    | 16 bi                 | t address                                        | Store data in B to memory loca<br>addressing)                    | ition addr (e: | xtended     | 5              |  |  |  |

| 8             | LDX #data        | 3    | 16 bi                 | t data                                           | Load X with immediate data (i                                    | mmediate ad    | dr.)        | 4              |  |  |  |

| 9             | LDX #data        |      |                       | t data                                           | Load Y with immediate data (i                                    |                |             | 4              |  |  |  |

| Ā             | LDT #date        |      |                       | taddr                                            | Load X with data from memor                                      |                |             | 6              |  |  |  |

|               |                  |      |                       |                                                  | (extended addressing)                                            |                |             | _              |  |  |  |

| В             | LDY addr         |      | 16 bi                 | t addr                                           | Load Y with data from memor<br>(extended addressing)             | y location ad  | ldr.        | 6              |  |  |  |

| С             | LDAA dd,         | х    | 8 bit                 | acement                                          | Load A with data from memor<br>by X + dd (indexed address        |                | ointed to   | 4              |  |  |  |

| D             | LDAA dd,         | v    | 8 bit                 |                                                  | Load A with data from memor                                      | v location po  | vinted to   | 4              |  |  |  |

|               |                  |      | displ                 | acement                                          | by Y + dd (indexed address                                       | sing)          |             |                |  |  |  |

| E             | LDAB dd,         | х    | 8 bit<br>displ        | acement                                          | Load B with data from memory<br>by X + dd (indexed address       | ing)           |             | 4              |  |  |  |

| F             | LDAB dd,         | Y    | 8 bit                 |                                                  | Load B with data from memory<br>by Y + dd (indexed address       | y location po  | inted to    | 4              |  |  |  |

| 10            | STAA dd,2        | x    | 8 bit                 |                                                  | Store data in A to memory loca<br>+ dd (indexed addressing)      | ation pointed  | to by X     | 4              |  |  |  |

| 11            | STAA dd,         | v    | displacement<br>8 bit |                                                  | Store data in A to memory location pointed to by Y               |                |             |                |  |  |  |

| 11            | STAA dd,         | ĩ    |                       | acement                                          | + dd (indexed addressing)                                        |                |             |                |  |  |  |

| 12            | STAB dd.3        | v    | 8 bit                 |                                                  | Store data in B to memory location pointed to by X +             |                |             |                |  |  |  |

|               |                  |      | displ                 | acement                                          | dd (indexed addressing)                                          |                | 4           |                |  |  |  |

| 13            | STAB dd,         | Y    | 8 bit<br>displ        | acement                                          | Store data in B to memory loca<br>dd (indexed addressing)        | to by Y +      | 4           |                |  |  |  |

| 14            | SUM BA           | nor  |                       | Sum A D                                          | and place in A (inherent addressing                              | ) 2            |             |                |  |  |  |

| 14            | SUM_BA           | noi  |                       |                                                  | and place in B (inherent addressing                              | -              |             |                |  |  |  |

| 16            | AND_BA           | nor  |                       |                                                  | and place in A (inherent addressing                              |                | -           |                |  |  |  |

| 17            | AND_AB           | nor  |                       |                                                  | and place in B (inherent addressing                              |                | _           |                |  |  |  |

| 18            | OR_BA            | nor  |                       |                                                  | nd place in A (inherent addressing)                              |                | _           |                |  |  |  |

| 19            | OR_AB            | nor  |                       |                                                  | nd place in B (inherent addressing)                              | 2              | -           |                |  |  |  |

| 13            | COMA             | nor  |                       |                                                  | nt contents in A (inherent addressing)                           |                | _           |                |  |  |  |

| 18            | COMB             | nor  |                       | Compleme                                         | nt contents in B (inherent addressin                             | 1g) 2          | _           |                |  |  |  |

| 1D<br>1C      | SHFA_L           | nor  |                       | Shift A left                                     | t by one bit (inherent addressing)                               | 2              | _           |                |  |  |  |

| 1D            | SHFA_R           | nor  |                       | Shift A riel                                     | ht by one bit (inherent addressing)                              | 2              | _           |                |  |  |  |

| 1D<br>1E      | SHFB L           |      |                       |                                                  | by one bit (inherent addressing)                                 | 2              | _           |                |  |  |  |

| 1E<br>1F      | SHFB_L<br>SHFB_R |      |                       |                                                  | t by one bit (inherent addressing)                               | 2              |             |                |  |  |  |

| 30            | INX              | _    |                       |                                                  |                                                                  | 2              | -           |                |  |  |  |

| 31            | INX<br>INY       | noi  |                       | · · · · · · · · · · · · · · · · · · ·            |                                                                  |                |             |                |  |  |  |

| 20            |                  | addr | rL                    | Branch if A -                                    | - 0, i.e., Z Flag – 1 (absolute                                  | 3              |             |                |  |  |  |

| 21            | BNE              | addr | rL :                  |                                                  | ± 0, i.e., Z Flag − 0 (absolute                                  | 3              |             |                |  |  |  |

| 22            | BN               | addr | rL :                  | addressing)<br>Branch if A i<br>(absolute add    | s negative, i.e., N Flag – 1                                     | 3              |             |                |  |  |  |

| 23            | BP               | addr | rL I                  | (absolute add<br>Branch if A is<br>(absolute add | s positive (or zero), i.e., N Flag – 0                           | 3              |             |                |  |  |  |

|               |                  |      | 1                     | aosointe add                                     | (cound)                                                          |                |             |                |  |  |  |

Special Notes

<sup>and N flag are only set and cleared by the contents in register A.

A branch is accomplished by moving the operand address "addr" to the lower byte of the PC. The upper byte of the PC remains unchanged after a branch.

The Branch Instructions use absolute addressing where only the low byte of the address is used as an operand. If the branch condition is met, the high byte of the PC is unchanged and the low byte takes the value of the operand (addrL).</sup>

EEL 3701 – Digital Logic & Computer Systems Final Exam – Fall Semester 2007

Name:

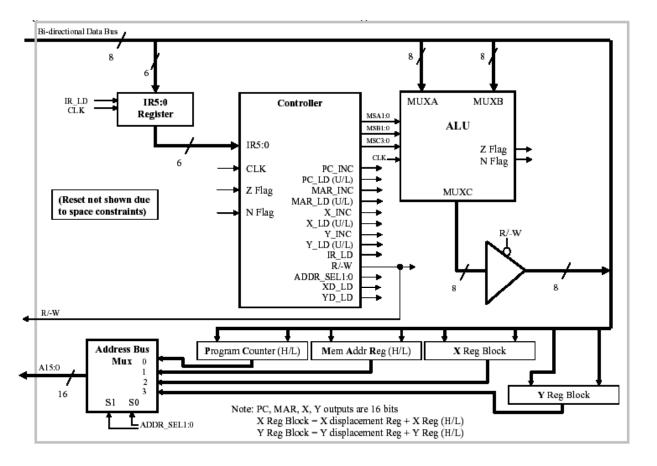

# **GCPU Block Diagram**

| MSA1/<br>MSB1 | MSA0/<br>MSB0 | Bus Selected as Input<br>to REGA/REGB |

|---------------|---------------|---------------------------------------|

| 0             | 0             | INPUT Bus                             |

| 0             | 1             | REGA Output Bus                       |

| 1             | 0             | REGB Output Bus                       |

| 1             | 1             | OUTPUT Bus                            |

| MSC2:0 | Action                                     |

|--------|--------------------------------------------|

| 000    | REGA Bus to OUTPUT Bus                     |

| 001    | REGB Bus to OUTPUT Bus                     |

| 010    | complement of REGA Bus to OUTPUT Bus       |

| 011    | bit wise AND REGA/REGB Bus to OUTPUT Bus   |

| 100    | bit wise OR REGA/REGB Bus to OUTPUT Bus    |

| 101    | sum of REGA Bus & REGB Bus to OUTPUT Bus   |

| 110    | shift REGA Bus left one bit to OUTPUT Bus  |

|        | shift REGA Bus right one bit to OUTPUT Bus |

| 111    | (without sign extension)                   |

Name:\_\_\_\_\_

# Partial GCPU Next State Table

|            |         |       |            |      |          | R    |         | REG | ADDR |      |     | X,Y |             | Disp     |        |                           |

|------------|---------|-------|------------|------|----------|------|---------|-----|------|------|-----|-----|-------------|----------|--------|---------------------------|

| Pres State | Opcode  | Flags | Next State |      | Mux Sele | ct   | Control |     | INC  | SEL  | PC  | MAR | MAR Loading |          | Regs   |                           |

|            |         |       |            |      |          |      |         |     | PC   | ADDR | PC  | MAR | x           | Ŷ        |        |                           |

|            |         |       |            | MSA  | MSB      | MSC  | IR      | R   | MAR  | SEL  | LD  | LD  | LD          | LD       | XD_LD  |                           |

| Q[50]      | IR[50]  | ZN    | D[50]      | [10] | [10]     | [30] | LD      | /W  | XY   | [10] | L/U | L/U | L/U         | L/U      | YD_LD  | Present State Function    |

| 000000     | XXXXXX  | XX    | 000001     | 01   | 10       | 0000 | 1       | 1   | 0000 | 00   | 00  | 00  | 00          | 00       | 00     | generic instruction fetch |

| 000001     | 000000  | XX    | 000000     | 01   | 01       | 0000 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | - 00     | 00     | Transfer A to B (TAB)     |

| 000001     | 000001  | XX    | 000000     | 10   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | - 00     | 00     | Transfer B to A (TBA)     |

| 000001     | 000010  | XX    | 000010     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | - 00     | 00     | LDAA #data, state 1       |

| 000010     | XXXXXX  | XX    | 000000     | 00   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | - 00     | 00     | LDAA #data, state 2       |

| 000001     | 000011  | XX    | 000011     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | - 00     | 00     | LDAB #data, state 1       |

| 000011     | XXXXXX  | XX    | 000000     | 01   | 00       | 0001 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | - 00     | 00     | LDAB #data, state 3       |

| 000001     | 000100  | XX    | 000100     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | - 00     | 00     | LDAA addr, state 1        |

| 000100     | XXXXXX  | XX    | 000101     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 10  | 00          | 00       | 00     | LDAA addr, state 4        |

| 000101     | XXXXXX  | XX    | 000110     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 01  | 00          | 00       | 00     | LDAA addr, state 5        |

| 000110     | XXXXXX  | XX    | 000000     | 00   | 10       | 0000 | 0       | 1   | 0000 | 01   | 00  | 00  | 00          | 00       | 00     | LDAA addr, state 6        |

| 000001     | 000101  | XX    | 000111     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | 00       | 00     | LDAB addr, state 1        |

| 000111     | XXXXXX  | XX    | 001000     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 10  | 00          | 00       | 00     | LDAB addr, state 7        |

| 001000     | XXXXXX  | XX    | 001001     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 01  | 00          | 00       | 00     | LDAB addr, state 8        |

| 001001     | XXXXXX  | XX    | 000000     | 01   | 00       | 0000 | 0       | 1   | 0000 | 01   | 00  | 00  | 00          | 00       | 00     | LDAB addr, state 9        |

| 000001     | 000110  | XX    | 001010     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | 00       | 00     | STAA addr, state 1        |

| 001010     | XXXXXX  | XX    | 001011     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 10  | 00          | 00       | 00     | STAA addr. state A        |

| 001011     | XXXXXX  | XX    | 001100     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 01  | 00          | 00       | 00     | STAA addr, state B        |

| 001100     | XXXXXX  | XX    | 000000     | 01   | 10       | 0000 | 0       | 0   | 0000 | 01   | 00  | 00  | 00          | 00       | 00     | STAA addr, state C        |

| 000001     | 000111  | XX    | 001101     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | 00       | 00     | STAB addr, state 1        |

| 001101     | XXXXXX  | XX    | 001110     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 10  | 00          | 00       | 00     | STAB addr, state D        |

| 001110     | XXXXXX  | XX    | 001111     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 01  | 00          | 00       | 00     | STAB addr, state E        |

| 001111     | XXXXXX  | XX    | 000000     | 01   | 10       | 0001 | 0       | 0   | 0000 | 01   | 00  | 00  | 00          | 00       | 00     | STAB addr, state F        |

|            |         |       |            |      |          |      |         |     |      |      |     |     |             |          |        |                           |

| 000001     | 010100  | XX    | 000000     | 11   | 10       | 0010 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | 00       | 00     | SUM BA state 1            |

| 000001     | 010101  | XX    | 000000     | 01   | 11       | 0010 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | 00       | 00     | SUM AB state 1            |

| 000001     | 010110  | XX    | 000000     | 11   | 10       | 0011 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | 00       | 00     | AND BA state 1            |

| 000001     | 010111  | XX    | 000000     | 01   | 11       | 0011 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | 00       | 00     | AND AB state 1            |

|            |         |       |            |      |          |      |         |     |      |      |     |     |             | the file | 107.50 |                           |

| 000001     | 100011  | X0    | 110010     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | 00       | 00     | BP addr state 1           |

| 000001     | 100011  | XI    | 110010     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | 00       | 00     | BP addr state 1           |

| 110010     | XXXXXX  | XX    | 000000     | 01   | 10       | 0000 | 0       | 1   | 0000 | 00   | 10  | 00  | 00          | 00       | 00     | BP addr state 32          |

| 110011     | XXXXXXX | XX    | 000000     | 01   | 10       | 0000 | 0       | 1   | 1000 | 00   | 00  | 00  | 00          | 00       | 00     | BP addr state 33          |

| 000001     | 110000  | XX    | 000000     | 01   | 10       | 0000 | 0       | 1   | 1010 | 00   | 00  | 00  | 00          | 00       | 00     | Increment X (INX)         |

| 000001     | 110001  | XX    | 000000     | 01   | 10       | 0000 | 0       | 1   | 1010 | 00   | 00  | 00  | 00          | 00       | 00     | Increment Y (INY)         |

| 10000      | 110001  | AA    | 00000      | 01   | 10       | 0000 | 0       | 1   | 1001 | 00   | 00  | 00  | 00          | 00       | 00     | increment r (IN Y)        |