| EEL3701 - Dr. Gugel |

|---------------------|

| Spring 2017         |

| Exam #1             |

18 points

Page 3)

| Last Name, First Name |  |

|-----------------------|--|

|                       |  |

17 points

| UF ID# |  |  |  |

|--------|--|--|--|

Open book and open notes, 90-minute examination. No electronic devices are permitted.

Page 4)

| Page 1) | 9 points | <br>Page 2) | 23 points |  |

|---------|----------|-------------|-----------|--|

|         |          |             |           |  |

**Re-grade requests must be handed in the day exams are returned in class.** Write the problem number you wish reviewed. **A maximum of three review problems is allowed.** Do not write anywhere else on the exam other than below or you will receive a zero on the exam.

1. Directly synthesize a circuit for the following equation using only 2 Input NOR gates only. (9 pt.)

$$Y = \overline{A^*} \, (\overline{B^*C}) + E + \overline{D} \qquad \text{; A.L, B.H, C.L, D.H, E.L, Y.H} \quad \text{Do Not Simplify the Equation!}$$

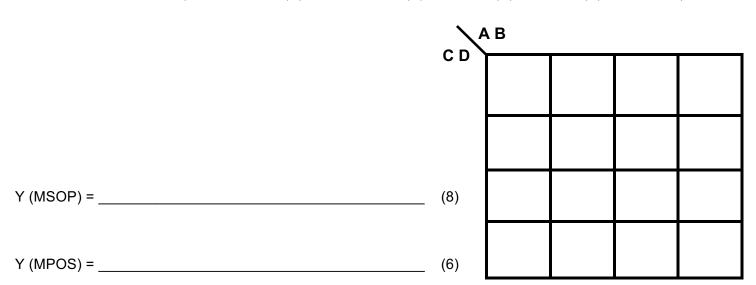

2. Find the **minimum sum of products** and **minimum product of sums** for the logic equation below using a K-Map. (14 pt.)

$$Y = (A+B+C+D)(/A+/B+C+D)(/A+C+D)(B+/C+D)(A+/B+/D)$$

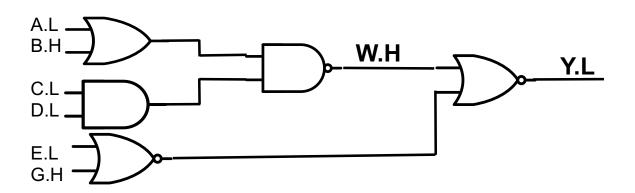

3. Derive the logic equations for the following signals listed after the circuit below. **Show all intermediate** signals as HIGH true for partial credit purposes. **DO NOT SIMPLIFY YOUR ANSWER!**

W.H = \_\_\_\_\_\_(5 pt.)

Y.L = \_\_\_\_\_\_(4 pt.)

| $Y = (X+Y+Z)(\overline{X}+\overline{Y}+\overline{W})(X-\overline{Y}+\overline{W})$                                | +Z+W)(X+Z)(X+Z+W)(X+Y+Z)                                                                            |

|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

|                                                                                                                   |                                                                                                     |

|                                                                                                                   |                                                                                                     |

|                                                                                                                   |                                                                                                     |

|                                                                                                                   |                                                                                                     |

|                                                                                                                   |                                                                                                     |

|                                                                                                                   |                                                                                                     |

|                                                                                                                   |                                                                                                     |

|                                                                                                                   |                                                                                                     |

|                                                                                                                   |                                                                                                     |

|                                                                                                                   |                                                                                                     |

| Y =                                                                                                               | MSOP                                                                                                |

| 5. A student would like to design a <b>multiplier</b> that <b>bit unsigned number</b> . i.e. P = M1:0 x N2:0 ;whe | computes the product of a <b>2 bit unsigned number</b> times a sere all numbers are unsigned binary |

| How many bits are required for P?                                                                                 | (2 pt.)                                                                                             |

| Write the Canonical Sum of Products (CSOP) for N2:0 below. (8 pt.)                                                | or the <b>most significant bit of P</b> based on inputs <b>M1:0</b> and                             |

|                                                                                                                   |                                                                                                     |

## 6 – 8. Perform the following addition, subtraction and multiplication. (9 pt.)

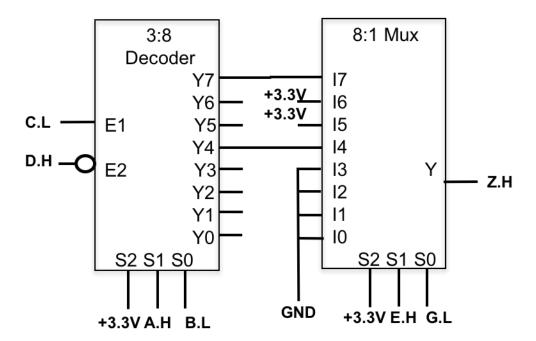

## 9. For the circuit below, derive the logic equation for Z.H. **Do not Simplify!** (8 pt.)

Z.H = \_\_\_\_\_

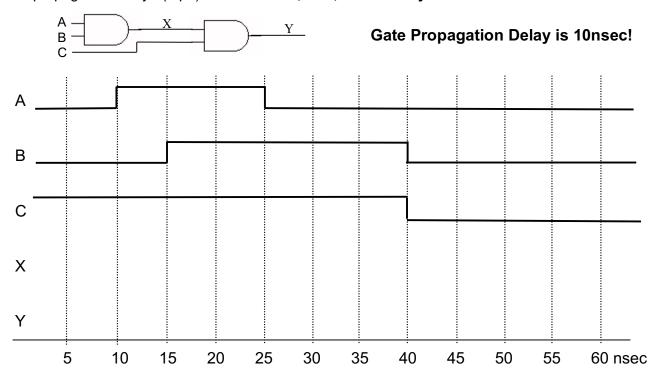

10. Given the circuit below complete the voltage timing diagram for signals X and Y. Assume all devices have a **10nsec** propagation delay. (8 pt.) **Assume A=L, B=L, C=H initially.**

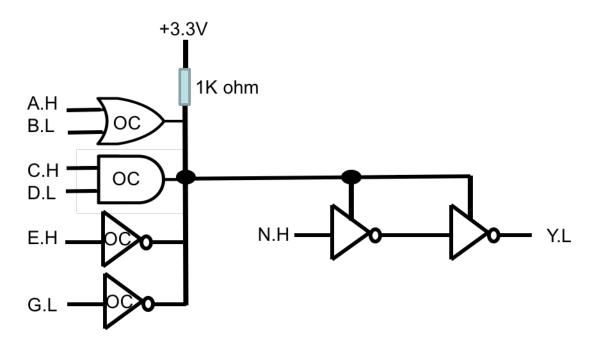

11. For the circuit below derive the *logic equation for* **Y** and *add the required missing Pull-up or Pull-down resistor* to make Y a function of A,B,C,D, E, G and N. (10 pt.)

Y.L =

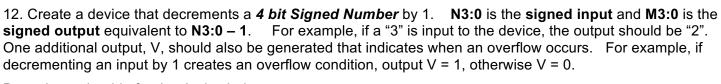

Draw the truth table for the device below:

N3 N2 N1 N0 M3 M2 M1 M0 V (10 pt.)

Derive the MSOP Logic Equation for **M0** and **V** (5 pt.):

Page 6 Page Score =