EEL 3701—Fall 2014 Wednesday, 15 October 2014

Page 1/12

Instructions:

front.

calculators.

•

#### Exam 1

Last Name, First Name

UF IEEE's SoutheastCon 2015 robot for Hardware Competition

Please read carefully.

- below.

- Failure to follow the below rules will result in <u>NO</u> partial credit

Read each question carefully and follow the instructions.

May the Schwartz be with you!

Turn off all *cell phones* and other *noise making*

<u>Show all work</u> on the <u>front</u> of the test papers. <u>Box</u> each answer. If you need more room, make a clearly indicated note on the front of the page, "**MORE ON BACK**", and use the back. The back of the page will <u>not</u> be graded without an indication on the

You may not use any notes, HW, labs, other books, or

The point values for problems may be changed at prof's discretion.

You must pledge and sign this page in order for a grade to be assigned.

devices and put away all electronics.

This exam counts for 20% of your total grade.

• The base (radix) of all number should be indicated with a subscript or prefix.

Put your name at the top of <u>this</u> test page (and, if you remove the staple, all others). Be sure your exam consists of <u>12</u> distinct pages. Sign your name and add the date

- *Truth tables, voltage tables, and timing simulations must be in counting order.*

- Label the inputs and outputs of each circuit with activation-levels.

- For each mixed-logic circuit diagram, label inputs of <u>each</u> gate with the appropriate logic equations.

- For K-maps, label *each* grouping with the appropriate equation.

- Labels inside of parts must be provided whenever it can be confusing, e.g., they **MUST** be specified for MUXes and Decoders, but not for NANDs and ORs.

- For each circuit design, equations must <u>not</u> be used as replacements for circuit elements.

- Boolean expression answers must be in lexical order, (i.e., /A before A, A before B, & D<sub>3</sub> before D<sub>2</sub>).

PLEDGE: On my honor as a University of Florida student, I certify that I have neither given nor received any aid on this examination, nor I have seen anyone else do so.

| Regrade comments below: Give page # and problem # and reason for the petition. | SIGN YO | UR NAME   |        |

|--------------------------------------------------------------------------------|---------|-----------|--------|

|                                                                                | Pages   | Available | Points |

|                                                                                | 2-3     | 14        |        |

|                                                                                | 4       | 3         |        |

|                                                                                | 5       | 13        |        |

|                                                                                | 6       | 7         |        |

|                                                                                | 7       | 13        |        |

|                                                                                | 8       | 12        |        |

|                                                                                | 9       | 11        |        |

|                                                                                | 10      | 11        |        |

|                                                                                | 11-12   | 16        |        |

|                                                                                | TOTAL   | 100       |        |

Good luck & Go Gators!!!

priate logic equations. ey **MUST** be specified fo elements.

| University of Florida                           |

|-------------------------------------------------|

| Department of Electrical & Computer Engineering |

EEL 3701—Fall 2014 Wednesday, 15 October 2014 Dr. Eric. M. Schwartz

Page 2/12

#### Exam 1

Last Name, First Name

| [14%] 1.      | Solve the following arithmetic problems.                   | Remember to show <u>ALL</u> work here and in  |

|---------------|------------------------------------------------------------|-----------------------------------------------|

|               | EVERY problem on this exam.                                |                                               |

| (4%)<br>4 min | a) Determine the unsigned hexadecimal, number $567_{10}$ . | octal, binary, and BCD representations of the |

|               |                                                            | Binary:                                       |

|               |                                                            | Octal:                                        |

|               |                                                            | Hex:                                          |

|               |                                                            | BCD:                                          |

(3%) b) Determine the **<u>12-bit</u>** signed magnitude, 1's complement, and 2's complement representations of the decimal number  $-567_{10}$ . (I strongly recommend that you check 3 min your work before moving on to the next problem.)

Signed Mag:

\_\_\_\_\_

1's Comp: \_\_\_\_\_

2's Comp: \_\_\_\_\_

c) What is  $-8_{10}$  in <u>4-bit</u> 2's complement? (Hint:  $2^3 = 8$ .) You must show <u>all</u> work.

(-8)<sub>2 4-bit 2's comp</sub>:

| (1%)  |  |

|-------|--|

| 1 min |  |

Page 3/12

#### Exam 1

Last Name, First Name

(2%) 1. c) What is  $-2048_{10} - 567_{10}$  in <u>12-bit</u> 2's complement? (Hint:  $2^{11} = 2048$ .) You must use binary numbers to <u>derive</u> and determine the solution (not decimal). You must show <u>all</u> work.

(-2048<sub>10</sub> - 567<sub>10</sub>)<sub>2 12-bit 2's comp:</sub>

(2%) 1. d) What is  $1024_{10} - 567_{10}$  in <u>12-bit</u> 2's complement? ? (Hint:  $2^{10} = 1024$ .) You must use binary numbers to <u>derive</u> and determine the solution (not decimal). You must show <u>all</u> work.

(1024<sub>10</sub> - 567<sub>10</sub>)<sub>2 12-bit 2's comp:</sub>

(2%) 1. e) Perform the requested operations in binary. Show 4 digits after the binary point and 1 digit after the hex point. What is the answer in both **binary** and **hex**?

$1101.11 \div 100$

Page 4/12

## Exam 1

Last Name, First Name

[3%] 2. Simplify the following logic equation using <u>only Boolean identities, laws or theorems</u>.

[5 min] Show all steps. Give the solution in MSOP form.

$$Ga = \overline{\left(T + \overline{\overline{O}} + R\right)} * \overline{\left(\overline{T} + \overline{\overline{S}OR}\right)}$$

*Ga* = \_\_\_\_\_

Page 5/12

(3%)

#### Exam 1

Last Name, First Name

- [13%] 3. Answer the following questions.

- a) Sketch the bdf file so that it looks like what you would create in Quartus for the equation Y = /(A + /B) with A(H), B(L), Y(H) using the <u>minimum number</u> of gates. 4 min

d) Draw a **layout** of the entire above circuit **including** each (3%) of the switch and LED circuits for part c and the logic 5 min 14-pin Chip from **part a**. A layout shows each of the parts as they appear on the breadboard. Include the needed switches, resistors (SIP and/or DIP), and LEDs. I don't know what chip you used, so assume whatever pin numbers you want (for the 14-pin chip), along with the **<u>normal</u>** power and ground pins. Label the pin numbers in part b. Label the wires for each of the inputs and outputs (A, B, and Y) with their activation levels. I suggest that you use labels to replace long wires. The dark part of the switches in the figure are the parts that you move to change the switch's closure state. Draw the switches in their **true** positions. Vcc

University of Florida Department of Electrical & Computer Engineering EEL 3701—Fall 2014 Wednesday, 15 October 2014

Exam 1

Last Name, First Name

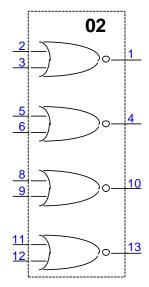

[7%] 4. Directly implement the below equation with a mixed-logic circuit diagram. (Do NOT simplify the equation.) Use only gates of 74HC02 chips (or their mixed-logic equivalents). Use the minimum number of gates required. Use the appropriate mixed-logic symbols. You are free to choose the activation levels for all signals except that Gat (the output) must be <u>active-low</u>. Label the parts and pin <u>numbers</u> for your circuit design.

$$Gat = \left(\left\{\overline{\left[(O+\overline{R})*\overline{G}\right]} + \overline{R}\right\}*\overline{\left[O*\overline{W}\right]}\right) + L$$

Page 6/12

- R( )\_\_\_\_

- G( )\_\_\_\_

- R( )\_\_\_\_

- O( )\_\_\_\_

- W( )\_\_\_\_

- L( )\_\_\_\_

Page 7/12

### Exam 1

Last Name, First Name

[5%] 5. Use only open-collector gates (of any real SSI-type gate) to directly implement the below equation. (Do NOT simply the equation.) Show your work! *M* must be active-high and *U* must be active-low, but you may chose all other activation levels.

$$Beat = (M + \overline{I} + \overline{Z}) * \overline{(Z + \overline{O} + U)}$$

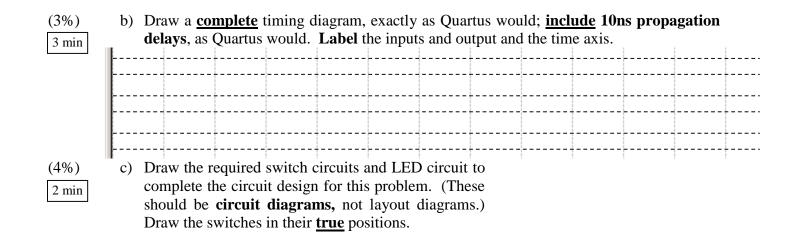

[8%] 6. Determine the sequence of outputs, for  $Q_2(H)$ ,  $Q_1(H)$ , and  $Q_0(H)$ , starting at  $Q_2Q_1Q_0=000$ . Assume the asynchronous clear, CLR(L), is false and a series of clocks (CLK) occur to create the sequence of outputs. Show **ALL** work. List the next **7 values** in the sequence.

Sequence =

Page 8/12

## Exam 1

Last Name, First Name

O(H)

0 1

3 E

¢,

R(H)

R(L)

R(H)

4-input MUX with

non 3-state Enable

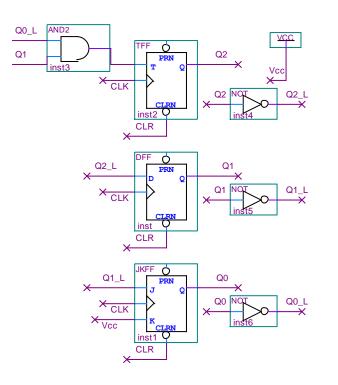

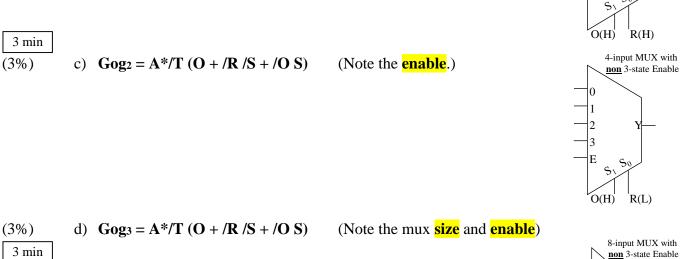

Use the given multiplexers to design mixed-logic circuit diagrams that solve each of the [12%] 7. below problems. Be careful to read the equation correctly. Choose activation levels for 2 min each signal (that has not already been assigned) to **minimize** the number of additional parts required. Use the minimum number of additional SSI gates. Show all work. (The four below problems are *independent*.)

$$\frac{3 \text{ min}}{(3\%)}$$

a)  $Gog_0 = A^*/T (O + /R /S + /O S)$

$$\frac{3 \text{ min}}{(3\%)}$$

b)  $Gog_1 = A^*/T (O + /R /S + /O S)$  (Note the enable.)

|                  | Jniversity of Florida<br>Department of Electrical & Computer Engineering                   | EEL 3701—Fall 2014<br>Wednesday, 15 October 2014                             | Dr. Eric. M. Schwartz                               |

|------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------|

| F                | Page 9/12                                                                                  | Exam 1                                                                       |                                                     |

|                  |                                                                                            | Last Name                                                                    | , First Name                                        |

| [11%] 8          | 3. Solve the following Karnaugh M                                                          | ap Boolean Algebraic simplifications p                                       | roblems.                                            |

| (6%)             | a) Simply the below equation ar                                                            | nd put the result in MSOP <u>and</u> form MI                                 | POS. <mark>Label</mark> your circles!               |

| 8 min            | $X = (\overline{A} + \overline{B} + \overline{C} + D) * (\overline{A} + B - \overline{C})$ | $(A + \overline{B} + \overline{C}) * (A + \overline{C} + D)$                 | $*(\overline{B}+\overline{C}+\overline{D})*(A+B+C)$ |

|                  | CD                                                                                         | CD                                                                           |                                                     |

| AB               | CD                                                                                         | AB                                                                           |                                                     |

|                  |                                                                                            |                                                                              |                                                     |

|                  |                                                                                            |                                                                              |                                                     |

|                  |                                                                                            |                                                                              |                                                     |

|                  |                                                                                            |                                                                              |                                                     |

|                  |                                                                                            |                                                                              |                                                     |

| Y <sub>MSO</sub> |                                                                                            | $Y_{MPOS} =$                                                                 |                                                     |

| - 1050           | <u>, , , , , , , , , , , , , , , , , , , </u>                                              | - WI 05                                                                      |                                                     |

|                  |                                                                                            |                                                                              |                                                     |

| (4%)             |                                                                                            | 001, and 1101, i.e., the textbook's d(<br>ew MSOP <b>and</b> MPOS equations. | 8,9,13), are <b>DON'T</b>                           |

| 4 min            |                                                                                            |                                                                              |                                                     |

|                  | CD                                                                                         | CD                                                                           |                                                     |

| AE               |                                                                                            | AB                                                                           |                                                     |

|                  |                                                                                            |                                                                              |                                                     |

|                  |                                                                                            |                                                                              |                                                     |

|                  |                                                                                            |                                                                              |                                                     |

|                  |                                                                                            |                                                                              |                                                     |

|                  |                                                                                            |                                                                              |                                                     |

| Y <sub>MSC</sub> | $_{\rm OP} =$                                                                              | $Y_{MPOS} =$                                                                 |                                                     |

|                  |                                                                                            |                                                                              |                                                     |

(1%) c) Are the above equations (in part b) equivalent? Why or why not?

2 min

University of Florida Department of Electrical & Computer Engineering EEL 3701—Fall 2014 Wednesday, 15 October 2014

Page 10/12

# Exam 1

Last Name, First Name

| [11%] 9. | Solve   | the | below | decoder-related |

|----------|---------|-----|-------|-----------------|

|          | problem | ns. |       |                 |

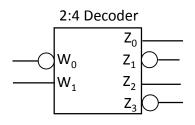

(4%) a) Determine the truth table for the below decoder. Also create a functional block diagram from the given block diagram.

|  | r |  |  |   |

|--|---|--|--|---|

|  |   |  |  |   |

|  |   |  |  |   |

|  |   |  |  |   |

|  |   |  |  |   |

|  |   |  |  |   |

|  |   |  |  | - |

|  |   |  |  | - |

|  |   |  |  | - |

|  |   |  |  |   |

|  |   |  |  |   |

|  |   |  |  |   |

b) Determine the equations for the decoder (use space above). Simplify the equations. Design a circuit (use space below) to implement this design. Use only SSI gates.

(3%)

c) Add an active-low enable to the above truth table (on the left) and complete the table. (It is not necessary to put this **augmented table** in counting order.). Add to (but do **NOT** modify) the above circuit for the new design. Use the signal names in part b in your design below. Rename the **new** outputs P<sub>3</sub> through P<sub>0</sub>.

Page 11/12

### Exam 1

Last Name, First Name

- [16%] 10. Design the following specified multiplexers.

- (4%) a) Create a functional block diagram and then design a 4-input multiplexer (with no enable). For this design, use only 2-input multiplexers with no enables. Only if necessary, you may use SSI parts to complete your design. Use the minimum number of MUXs.

- (4%)

- 4 min

- b) Create a functional block diagram and then design a 4-input multiplexer with a non tri-state enable. For this design, use only 2-input multiplexers with non tri-state enables. (All enables can have any activation-level.) Only if necessary, you may use SSI parts to complete your design. Use the minimum number of MUXs.

Page 12/12

Exam 1

Last Name, First Name

10 c) Create a functional block diagram and then design a 4-input multiplexer with no (4%) enable. For this design, use only 2-input multiplexers with tri-state enables. (All 4 min enables can have any activation-level.) Only if necessary, you may use SSI parts to complete your design. Use the minimum number of MUXs.

(4%)d) Create a functional block diagram and then design a 4-input multiplexer with a tristate enable. For this design, use only 2-input multiplexers with tri-state enables. (All 4 min enables can have any activation-level.) **Only** if necessary, you may use SSI parts to complete your design. Use the minimum number of MUXs.