| University of Florida                           |

|-------------------------------------------------|

| Department of Electrical & Computer Engineering |

EEL 3701—Summer 2012 Tuesday, 10 July 2012

Dr. Eric. M. Schwartz

Page 1/13

|       | - |

|-------|---|

| 1'    |   |

| HVIII |   |

|       |   |

|       |   |

Last Name, First Name

#### Instructions:

- Turn off all <u>cell phones</u>, <u>beepers</u> and other noise making devices.

- <u>Show all work</u> on the <u>front</u> of the test papers. <u>Box</u> each answer. If you need more room, make a clearly indicated note on the front of the page, "MORE ON BACK", and use the back. The back of the page will <u>not</u> be graded without an indication on the front.

- This exam counts for 33% of your total grade.

Good morning! Welcome!

- Read each question carefully and follow the instructions.

- You may <u>not</u> use any notes, HW, labs, other books, or calculators.

- The point values for problems may be changed at prof's discretion.

- Please read carefully.

- You must pledge and sign this page in order for a grade to be assigned.

- Put your name at the top of <u>this</u> test page (and, if you remove the staple, all others). Be sure your exam consists of <u>13</u> distinct pages. Sign your name and add the date below.

- For each circuit design, equations must <u>not</u> be used as replacements for circuit elements.

- For each mixed-logic circuit diagram, label inputs of each gate with the appropriate logic equations

- *Truth tables and voltage tables must be in counting order.*

- order.

Good luck & Go Gators!!!

- Label the inputs and outputs of each circuit with activation-levels.

- Boolean expression answers must be in **lexical order**,( i.e., /A before A, A before B, &  $D_3$  before  $D_2$ ).

- For K-maps, label <u>each</u> grouping with the appropriate equation.

PLEDGE: On my honor as a University of Florida student, I certify that I have neither given nor received any aid on this examination, nor I have seen anyone else do so.

| SIGN YOUR NAME | DATE (10 July 2012) |

|----------------|---------------------|

| Regrade comments below: | : Give page # and problem # and reason for the petition. |

|-------------------------|----------------------------------------------------------|

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

|                         |                                                          |

| Page  | Available | Points |

|-------|-----------|--------|

| 2-3   | 18        |        |

| 4     | 14        |        |

| 5     | 11        |        |

| 6     | 8         |        |

| 7     | 10        |        |

| 8     | 10        |        |

| 9-11  | 18        |        |

| 12-13 | 11        |        |

| TOTAL | 100       |        |

Page 2/13

|            | _ |

|------------|---|

| 17-7-0-7-0 | 1 |

| H.V.HIII   |   |

| IJAGIII    |   |

Last Name, First Name

(37<sub>10</sub>+111<sub>10</sub>)<sub>2 8-bit 2's comp</sub>:

|               |    |                                                                                                              |      |       |           | Lastina     | me,    | r ii st ivaiii | C           |

|---------------|----|--------------------------------------------------------------------------------------------------------------|------|-------|-----------|-------------|--------|----------------|-------------|

| [14%] 1.      |    | olve the following arithmetic problems. <b>R VERY problem on this exam.</b>                                  | eme  | ember | to show   | ALL v       | vork ł | nere and       | d in        |

| (4%) 3 min    | a) | Determine the unsigned hexadecimal, ocnumber $111_{10}$ .                                                    | tal, | binar | y, and BO | CD repr     | esenta | tions of       | the         |

|               |    |                                                                                                              |      |       | Binary:   |             |        |                |             |

|               |    |                                                                                                              |      |       | Octal:    |             |        |                |             |

|               |    |                                                                                                              |      |       | Hex:      |             |        |                |             |

|               |    |                                                                                                              |      |       | BCD:      |             |        |                |             |

| (3%) 2 min    | b) | Determine the <u>8-bit</u> signed magnitude representations of the decimal number -111                       |      | l's c | Signed l  | Mag:<br>ıp: |        | complen        |             |

| (2%) 1. 2 min | d) | What is $37_{10} + 111_{10}$ in <b>8-bit</b> 2's complem and determine the solution (not decimal). Figure 1. |      |       |           | -           |        |                | <u>rive</u> |

Page 3/13

(2%)

3 min

(2%)

2 min

# Exam 1

Last Name, First Name

(3%) 1. d) What is  $37_{10} - 111_{10}$  in <u>8-bit</u> 2's complement? You must use binary numbers to <u>derive</u> and determine the solution (not decimal). Remember that you must **show** <u>all</u> work.

$(37_{10} - 111_{10})_2$  8-bit 2's comp:

e) What is  $111_{10} - 37_{10}$  in <u>8-bit</u> 2's complement? You must use binary numbers to <u>derive</u> and determine the solution (not decimal). Remember that you must **show all work.**

$(111_{10} - 37_{10})_2$  8-bit 2's comp:

- [4%] 2. Answer the following short Quartus-related questions. Show <u>ALL</u> work.

- (2%) a) What is the difference between a timing simulation and a functional simulation?

b) If there are two inputs, A(L) and B(H), (written as A\_L and B\_H, respectively in a schematic entry [bdf] file), how does Quartus treat these signals of two different actuation levels, i.e., what are the differences on how Quartus uses them.

Page 4/13

| Fyam   | 1 |

|--------|---|

| CXAIII | 1 |

Last Name, First Name

| [14%] | 3. | Answer | the | following | questions.     |

|-------|----|--------|-----|-----------|----------------|

| [,~]  | •  |        |     |           | 9 00 0 0 110 1 |

(3%)2 min

(4%)

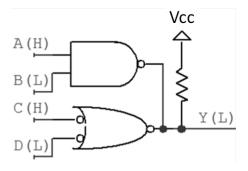

a) Sketch the bdf file so that it looks like what you would create in Quartus for the equation Y = /(A \* /B) with A(L), B(H), Y(L) using the **minimum number** of gates.

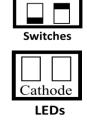

b) Draw a **complete** timing diagram, exactly as Quartus would; include 10ns propagation (3%)delays, as Quartus would. Label the inputs and output and the time axis. 3 min -----(4%)c) Draw the required switch circuits and LED circuit to complete the circuit design 2 min for this problem. (These should be circuit diagrams, not layout diagrams.) Draw the switches in their **true** positions.

d) Draw a layout of the entire above circuit including each of the switch and LED circuits for part c and the 5 min 14-pin Chip logic from part a. A layout shows each of the parts as they appear on the breadboard. Include the needed switches, resistors (SIP and/or DIP), and LEDs. I don't know what chip you used, so assume whatever pin numbers you want, along with the **normal** power and ground pins. Label the pin numbers in part a. Label the wires for each of the inputs and outputs (A, B, and Y) with their activation levels. I suggest that you use labels to replace long wires. The dark part of the switches in the figure are the parts that you move to change the switch's closure state. Draw the switches in their **true** positions.

| Vcc |   |  |  |  |  |  |  |  |  |  |  |  |  |  |

|-----|---|--|--|--|--|--|--|--|--|--|--|--|--|--|

|     |   |  |  |  |  |  |  |  |  |  |  |  |  |  |

|     | • |  |  |  |  |  |  |  |  |  |  |  |  |  |

Page 5/13

Last Name, First Name

[7%]

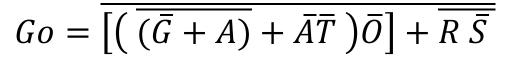

4. Directly implement the below equation with a mixed-logic circuit diagram. (Do <u>NOT</u> simplify the equation.) Use only gates of the 74HC00 (or their mixed-logic equivalents). Use the **minimum number of gates** required. Use the appropriate mixed-logic symbols. You are free to choose the activation levels. Label the pin <u>numbers</u> for your circuit design.

R( )\_\_\_

| S( | ) |  |

|----|---|--|

| •  |   |  |

Go()

[4%] 5. Find the MSOP or MPOS equivalent of the below Boolean expression. Show ALL work.

5 min

$$Go = \overline{\left[\left(\overline{(\overline{G} + A)} + \overline{R}\overline{T}\right)\overline{G}\right] + \overline{G}\overline{S}}$$

b)  $Y_1 = T*E*/B + O*/W*T$

8-input MUX

Page 6/13

(%)

# Exam 1

Last Name, First Name

[8%] 6. Use the given multiplexers to **design mixed-logic circuit diagrams** that solve each of the below problems. **Be careful to read the equation correctly.** Choose activation levels for each signal (that has not already been assigned) to **minimize** the number of additional parts required. Use the **minimum** number of additional SSI gates. Show all work. (The three below problems are independent.) For all of the problems, E, O and W are **active-high**. Choose efficient activation-levels for the other signals.

(%) a)  $\mathbf{Y_0} = \mathbf{T^*E^*/B} + \mathbf{O^*/W^*T}$  (Note the active-low  $\underline{\mathbf{NON}}$  tri-state enable.) 8-input MUX  $\begin{array}{c}

X_0 \\

X_1 \\

X_2 \\

X_3 \\

X_4 \\

X_5 \\

X_6 \\

X_7 \\

\end{array}$   $\begin{array}{c}

X_0 \\

X_1 \\

X_2 \\

X_3 \\

X_4 \\

X_5 \\

X_6 \\

X_7 \\

\end{array}$   $\begin{array}{c}

X_0 \\

X_1 \\

X_2 \\

X_3 \\

X_4 \\

X_5 \\

X_6 \\

X_7 \\

\end{array}$   $\begin{array}{c}

X_0 \\

X_1 \\

X_2 \\

X_3 \\

X_4 \\

X_5 \\

X_6 \\

X_7 \\

\end{array}$   $\begin{array}{c}

X_0 \\

X_1 \\

X_2 \\

X_3 \\

X_4 \\

X_5 \\

X_6 \\

X_7 \\

\end{array}$   $\begin{array}{c}

X_0 \\

X_1 \\

X_2 \\

X_3 \\

X_6 \\

X_7 \\

\end{array}$   $\begin{array}{c}

X_0 \\

X_1 \\

X_2 \\

X_3 \\

X_4 \\

X_5 \\

X_6 \\

X_7 \\

\end{array}$   $\begin{array}{c}

X_0 \\

X_1 \\

X_2 \\

X_3 \\

X_6 \\

X_7 \\

\end{array}$   $\begin{array}{c}

X_0 \\

X_1 \\

X_2 \\

X_3 \\

X_4 \\

X_5 \\

X_6 \\

X_7 \\

\end{array}$   $\begin{array}{c}

X_0 \\

X_1 \\

X_2 \\

X_2 \\

X_3 \\

X_4 \\

X_5 \\

X_6 \\

X_7 \\

\end{array}$   $\begin{array}{c}

X_0 \\

X_1 \\

X_2 \\

X_2 \\

X_3 \\

X_4 \\

X_5 \\

X_6 \\

X_7 \\

\end{array}$   $\begin{array}{c}

X_0 \\

X_1 \\

X_2 \\

X_2 \\

X_3 \\

X_4 \\

X_5 \\

X_7 \\

\end{array}$

(Note the active-**HIGH** enable.)

(%) c)  $\mathbf{Y_2} = /(\mathbf{T*E*/B} + \mathbf{O*/W*T})$  (Note the  $\underline{/}$  at beginning of equation.)

8-input MUX  $X_0$   $X_1$   $X_2$   $X_3$   $X_4$   $X_5$   $X_6$   $X_7$   $X_7$

Page 7/13

# Exam 1

10 min

Last Name, First Name

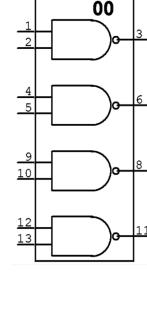

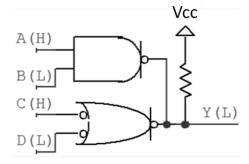

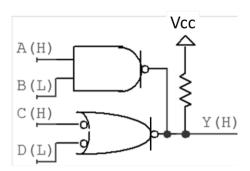

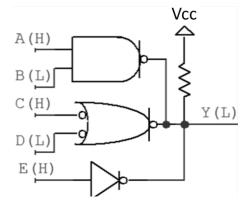

[10%] 7. Write the equations for the below circuits. Each equation should be given as a **sum-of-products** (MSOP) or a **product-of-sums** (MPOS) **Show your work!**

( %) a)

$Y_a = \underline{\hspace{1cm}}$

(%) b)

$Y_b = \underline{\hspace{1cm}}$

(%) c)

$Y_c =$

(%) d)

$Y_d = \underline{\hspace{1cm}}$

Page 8/13

## Exam 1

Last Name, First Name

[10%] 8. Use the below equation for this problem.

| $Y = \bar{A}\bar{B}\bar{C}\bar{D} + A\bar{B}\bar{D} + A\bar{B}\bar{C}D + \bar{A}CD + BC\bar{D} + \bar{A}\bar{B}C\bar{D}$ |

|--------------------------------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------------|

(7%)

7 min

a) Simply the below equation and put the result in MSOP <u>and</u> MPOS form. Are the solutions equivalent? Explain why or why not.

$Y_{MSOP} = Y_{MPOS} =$

Equivalent?:

(3%)

5 min

b) If the terms ABCD=1011 and ABCD=1111, i.e., the textbook's d(11,15), are **DON'T CAREs** (**X**), determine the new MSOP and MPOS equations. Are these solutions equivalent? Explain why or why not.

$Y_{MPOS} = Y_{MSOP} =$

Equivalent?:

Page 9/13

## Exam 1

Last Name, First Name

2 min

2 min

2 min

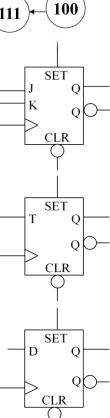

Design a system that counts as shown. The system must asynchronously reset to the state 000 when Start (active-high) goes true. Use a JK-FF for the most significant bit of your design, a T-FF for the least significant bit, and a D-FF(s) for any other bits you might need. An output, Fav (active-low), should be true if the count is either 3 or 7. The least-significant count bit, Q<sub>0</sub>, should be active-low; all other count bits must be active-high. Note: All the given FFs have asynchronous clear and set inputs and are shown below.

Start 000 011 111 100

(%)

2 min

a) Draw a functional **block diagram** (showing **all** the inputs, **all** the outputs, and the functional blocks). Put your design in a box with the inputs and outputs going into or out of the box, on the left or right, respectively. This is **not** a circuit diagram.

5 min

(%)

b) Complete the next-state **truth** table (**in counting order**).

|  |  |  |  |  |  | $\big] \ .$ |

|--|--|--|--|--|--|-------------|

|  |  |  |  |  |  | $\Big] \ .$ |

|  |  |  |  |  |  | ] .         |

|  |  |  |  |  |  | ╡.          |

|  |  |  |  |  |  | ͺͺ          |

|  |  |  |  |  |  | ╽.          |

|  |  |  |  |  |  | ╽.          |

|  |  |  |  |  |  | ╽.          |

|  |  |  |  |  |  | ١.          |

|  |  |  |  |  |  | ١٠          |

|  |  |  |  |  |  | ╢.          |

|  |  |  |  |  |  | ] .         |

University of Florida

Department of Electrical & Computer Engineering

EEL 3701—Summer 2012 Tuesday, 10 July 2012

Dr. Eric. M. Schwartz

Page 10/13

Exam 1

Last Name, First Name

(%) 9. c) Find the required **simplified** (MSOP or MPOS) equations.

7 min

| University of Florida                           |

|-------------------------------------------------|

| Department of Electrical & Computer Engineering |

### EEL 3701—Summer 2012 Tuesday, 10 July 2012

| Dr. | Eric. | M. | Schwartz |

|-----|-------|----|----------|

|     |       |    |          |

Page 11/13

| Fyam    | 1 |

|---------|---|

| TVXAIII |   |

Last Name, First Name

|                 | Last Name, First r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Name                           |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| (%) 9. d) 5 min | Design the complete circuit, <u>minimizing</u> the total number of components, but us JK-FF, T-FF, and D-FF(s) (if necessary), as described previously. All <b>input outputs</b> of the circuit should be <b>clearly indicated <u>coming into or out of</u></b> the below Your design must include the circuitry necessary to <b>asynchronous</b> re-start the sy "000" when the <b>Start</b> (active-high) signal goes true and show the active-low output when the output is $3_{10}$ or $7_{10}$ . | uts and<br>ow box.<br>ystem at |

| <u>Inputs</u>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Outputs                        |

Page 12/13

### Exam 1

Last Name, First Name

[11%] 10. In this problem you will design several multiplexers (MUX's).

( %)

2 min

a) Draw a functional block diagram of a 6-input MUX with no enable. The inputs should be labeled X and S (for select lines), both with proper subscripts, if necessary. The output should be labeled Y. All signals should be active-high.

(%)

10 min

b) Design **two different**, but functionally equivalent 6-input MUXs, both with **NO enable** using only 4-input and 2-input MUXs, with tri-state (T.S.) or non-tri-state (non-T.S.) enables of any activation-level. Use the two minimum cost solutions when the given MUX have the costs shown in the table. What are the costs for your two solutions? (The differences between the two designs should **not** be trivial differences.)

| Item                 | Cost |

|----------------------|------|

| 4-input T.S. MUX     | 20¢  |

| 4-input non-T.S. MUX | 18¢  |

| 2-input T.S. MUX     | 12¢  |

| 2-input non-T.S. MUX | 11¢  |

| University of Florida                           |

|-------------------------------------------------|

| Department of Electrical & Computer Engineering |

EEL 3701—Summer 2012 Tuesday, 10 July 2012

| Dr. E | ric. M. | Schw | artz |

|-------|---------|------|------|

|       |         |      |      |

Page 13/13

| Exam    | 1 |

|---------|---|

| LYXAIII |   |

Last Name, First Name

(%) 10 c) Modify one of your designs for the 6-input MUX without enable to make it a 6-input MUX with a NON-tri-state enable. Add as little extra cost as possible to create as low of a total cost as possible. Use ONLY the MUXs in the given table.

( %) 4 min d) Modify one of your designs for the 6-input MUX without enable to make it a 6-input MUX with a tri-state enable. Add as little extra cost as possible to create as low of a total cost as possible. Use ONLY the MUXs in the given table.