EEL 3701—Fall 2015 Thursday, 12 November 2015

Page 1/11

# Exam 2

Last Name, First Name

# Instructions: May the Schwartz. be with you!

- Turn off all <u>cell phones</u> and other noise making devices and put away <u>all electronics</u>.

- <u>Show all work</u> on the <u>front</u> of the test papers. <u>Box</u> each answer. If you need more room, make a clearly indicated note on the front of the page, "MORE ON BACK", and use the back. The back of the page will <u>not</u> be graded without an indication on the front.

- This exam counts for 20% of your total grade.

- Read each question *carefully* and *follow the instructions*.

- You may <u>not</u> use any notes, HW, labs, other books, or calculators.

- The point values for problems may be changed at prof's discretion.

- You must pledge and sign this page in order for a grade to be assigned.

- Put your name at the top of <u>this</u> test page (and, if you remove the staple, all others). Be sure your exam consists of <u>11</u> distinct pages. Sign your name and add the date below.

- Failure to follow the below rules will result in <u>NO</u> partial credit

- The base (radix) of all number should be indicated with a subscript or prefix.

- Truth tables, voltage tables, and timing simulations must be in counting order.

- Label the inputs and outputs of each circuit with activation-levels.

- For each mixed-logic circuit diagram, label inputs of each gate with the appropriate logic equations.

- For K-maps, label each grouping with the appropriate equation.

- Labels inside of parts must be provided whenever it can be confusing, e.g., they MUST be specified for MUXes and Decoders, but not for NANDs and ORs.

- For each circuit design, equations must not be used as replacements for circuit elements.

- Boolean expression answers must be in lexical order, (i.e., /A before A, A before B, & D3 before D2).

PLEDGE: On my honor as a University of Florida student, I certify that I have neither given nor received any aid on this examination, nor I have seen anyone else do so.

| SIGN YOUR NAME DATE (                                                          | 12 November 2015) |           |        |  |  |  |

|--------------------------------------------------------------------------------|-------------------|-----------|--------|--|--|--|

| Regrade comments below: Give page # and problem # and reason for the petition. | Page              | Available | Points |  |  |  |

| •                                                                              | 2-3               | 15        |        |  |  |  |

| •                                                                              | 4                 | 18        |        |  |  |  |

|                                                                                | 5-6               | 22        |        |  |  |  |

| •                                                                              | 7-8               | 20        |        |  |  |  |

|                                                                                | 9-11              | 25        |        |  |  |  |

| •                                                                              | TOTAL             | 100       |        |  |  |  |

| •                                                                              |                   |           |        |  |  |  |

Please read carefully.

Good luck & Go Gators!!!

University of Florida Department of Electrical & Computer Engineering EEL 3701—Fall 2015 Thursday, 12 November 2015

Page 2/11

# Exam 2

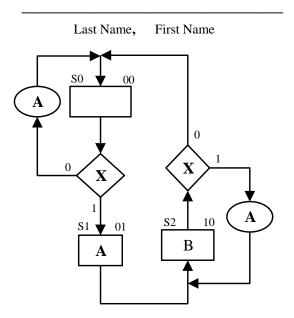

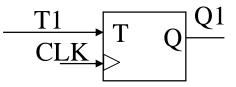

[15%] 1. In this problem you will ultimately design a circuit to implement this ASM. Use only SSI gates, a T-FF for the most significant state bit, a JK-FF for the least significant state bit, and D-FF's for any other FF's that you might need. The signals X and B are active- high and A is active-low. An active-low signal Go should asynchronously move the machine to state S2.

(%) a) Complete the next-state truth table. You may

<u>**not**</u> need all the rows and/or columns.

b) Find the required <u>simplified</u> (MSOP or MPOS) equations for determining the next state and for the outputs.

Page 3/11

#### Exam 2

Last Name, First Name

(%) 1. c) Design the complete mixed-logic circuit diagram, <u>minimizing</u> the total number of components, but using the T-FF and JK-FF (and D-FF(s), if necessary) as described previously. All inputs and outputs of the circuit should be clearly indicated <u>coming</u> into or out of the below box. Your design must include the circuitry necessary to asynchronously cause the system to go to state S2 when the Go (active-low) signal goes true. For debugging purposes, also output the active-low versions of the state bits.

| <u>Inputs</u> | , I | <u>Outputs</u> |

|---------------|-----|----------------|

|---------------|-----|----------------|

Page 4/11

#### Exam 2

Last Name, First Name

- [6%] 2. Answer the following questions about a state machine designed with one EEPROM, one J-K flip-flop, one T flip-flop, and any other necessary flip-flops of type D.

- (3%) a) What is the size of the EEPROM (addresses × data bits) if the state machine has 2 inputs,

- 3 min 7 outputs, and 5 states? Provide numbers only, i.e,  $37 \times 9$ , <u>NOT</u> expressions like  $3^7 \times \sqrt[4]{37}$ .

- (3%)b) What is the size of the EEPROM (addresses × data bits) if the state machine has 5 inputs,3 min2 outputs, and 9 states? Provide numbers only, i.e,  $37 \times 9$ , NOT expressions like  $3^7 \times \sqrt[4]{37}$ .

[4%] 3. Draw a complete mixed-logic circuit diagram including two switch circuits, one for an active-high input signal, U(H) and one for an active-low input, F(L), to generate the equation Go = U \* F. Draw the switches in their true positions. Draw an LED circuit for the active-high output, Go(H). Do NOT draw a layout.

[8%] 4. Answer the following short questions. (2%) a) What is VHDL?

Page 5/11

#### Exam 2

Last Name, First Name

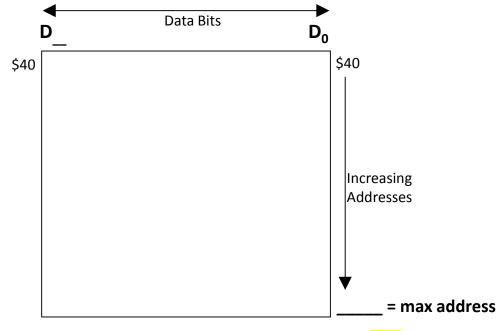

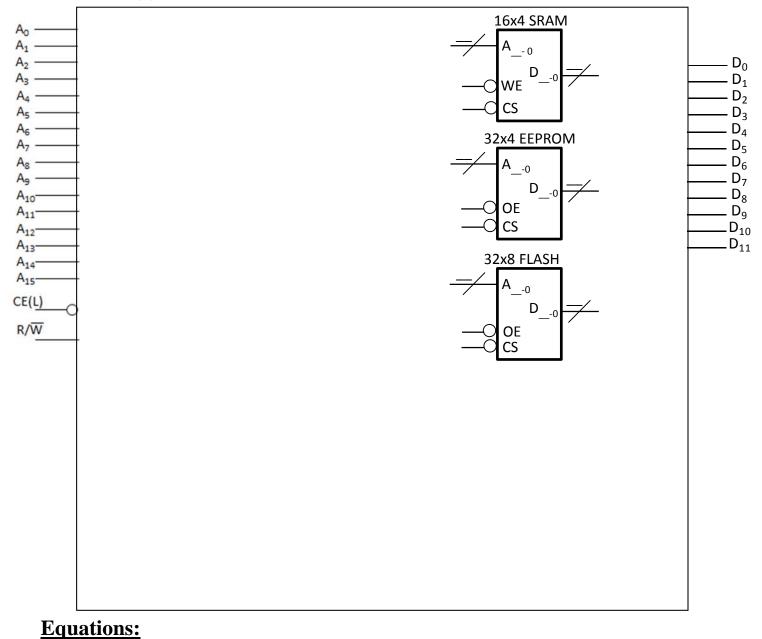

- [22%] 5. Given as many of each of the following as needed, design the memory module described 3 min below, with an active-low chip enable, CE(L): 16×4 SRAMs, 32×4 EEPROMs, and  $32\times8$  FLASH EEPROMs, The device should begin at address  $$40 = 40_{16}$  with 32x4 of SRAM at the <u>same addresses</u> as 32x4 EEPROM, followed immediately by 32×8 of FLASH. Add the minimum number of memory devices and the minimum number of additional SSI components required, i.e., other than the memory, <u>no</u> other MSI or LSI components are allowed.)

- (%) 5 min

(

a) Draw vertical and horizontal lines in the box below and label each resulting box with the memory type and size, using only the defined types and sizes given above. Also, fill in the subscript on the D at the top left and the maximum address at the bottom right.

b) What are the address and data ranges for <u>each</u> of the memory components drawn above (in binary and in hex)?

EEL 3701—Fall 2015 Thursday, 12 November 2015

Page 6/11

#### Exam 2

Last Name, First Name

(%) 8 min

%) 5. c) Design the required memory device circuit diagram below. Add the minimum number of <u>additional</u> memory components and SSI gates necessary (no MSI gates, LSI gates or PLDs). Add memory components and address and data subscripts as needed; <u>cross out</u> unneeded address and data pins. Use labels instead of wires for the design. <u>Also</u>, write the <u>equations</u> for each CS at the bottom of the page. Show all connections with either labels or wires (labels are <u>preferred</u>), just as in Quartus. Don't forget the system's active-low chip enable, CE, and R/~W [pronounced "read, write not," with R(H) and W(L)].

Page 7/11

#### Exam 2

Last Name, First Name

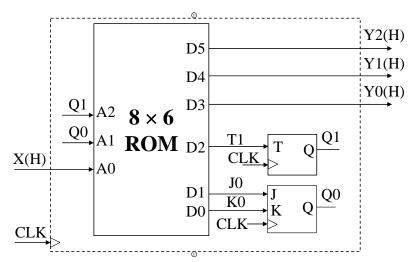

- [20%] 6. Use the below circuit diagram and the **ROM contents table** below to solve this problem. Note that the addresses and data in the table are in **hexadecimal** [base 16]. (This problem is very similar to a problem in homework 8 that was also done in class.) Note that a T-FF and a JK-FF are utilized in the below circuit.

- (17%) a) Derive the ASM chart for this circuit.

<u>17 min</u> Show <u>ALL</u> work, i.e., use at least part of the below table. You can draw your ASM on this page or on the next page.

|      | Contents of<br>ROM (Hex) |  |  |  |  |  |  |  |

|------|--------------------------|--|--|--|--|--|--|--|

| Addr | Data                     |  |  |  |  |  |  |  |

| 0    | 14                       |  |  |  |  |  |  |  |

| 1    | 14                       |  |  |  |  |  |  |  |

| 2    | 26                       |  |  |  |  |  |  |  |

| 3    | 26                       |  |  |  |  |  |  |  |

| 4    | <b>0</b> A               |  |  |  |  |  |  |  |

| 5    | 2A                       |  |  |  |  |  |  |  |

| 6    | 12                       |  |  |  |  |  |  |  |

| 7    | 02                       |  |  |  |  |  |  |  |

|      |                          |  |  |  |  |  |  |  |

|      |                          |  |  |  |  |  |  |  |

Page 8/11

### Exam 2

Last Name, First Name

(17%) 6. a) (Repeated from previous page.) Derive the ASM chart for this circuit. Show <u>ALL</u> work, i.e., use at least part of the above blank table. You can draw your ASM on this page or on the previous page.

(3%)

b) If the D2 pin of the ROM is broken, determine the necessary equation and circuit to input to the T-FF, i.e., create the proper input circuit for the T-FF.

Page 9/11

Exam 2

Last Name, First Name

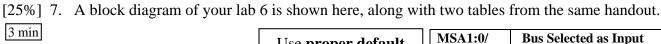

(6%) a) Assume that you can add two small additional circuits to the circuit described above. The purpose of these additional circuits is (1) to know when there would be an overflow when addition is used (output is V) and (2) to know when RegA is even (output is A\_Even). Hint: Zero is even. Show ALL work.

Page 10/11

## Exam 2

Last Name, First Name

5 min

(5%)

7. b) Get the average of the values in RegA and the number 3; put the resulting average in RegB. Use the values presently in RegA, i.e., 7. Describe your algorithm (plan) and then what is accomplished in each step. Use the minimum number of clock cycles. Give appropriate values for <u>ALL</u> signals. (Your algorithm should still work even if the two numbers, i.e., the 7 in A and the number 3 are changed.)

| # | MSA | MSB | MSC | Input | Cin | RegA | RegB | Output | Cout | RegA+ | RegB+ | Output+ | Cout+ |

|---|-----|-----|-----|-------|-----|------|------|--------|------|-------|-------|---------|-------|

| 1 |     |     |     |       |     | 0111 | 0000 |        |      |       |       |         |       |

| 2 |     |     |     |       |     |      |      |        |      |       |       |         |       |

| 3 |     |     |     |       |     |      |      |        |      |       |       |         |       |

| 4 |     |     |     |       |     |      |      |        |      |       |       |         |       |

| 5 |     |     |     |       |     |      |      |        |      |       |       |         |       |

| 6 |     |     |     |       |     |      |      |        |      |       |       |         |       |

(6%) 5 min

c) Multiply 3 by 5. (Your algorithm should still work even if the **number 3** is changed, but **not** if the number 5 is changed.) Store the result in **RegA**. Describe your algorithm (plan) and then what is accomplished in each step. Use the minimum number of clock cycles. Give appropriate values for <u>ALL</u> signals.

| # | MSA | MSB | MSC | Input | Cin | RegA | RegB | Output | Cout | RegA+ | RegB+ | Output+ | Cout+ |

|---|-----|-----|-----|-------|-----|------|------|--------|------|-------|-------|---------|-------|

| 1 |     |     |     |       |     | 1010 | 1011 |        |      |       |       |         |       |

| 2 |     |     |     |       |     |      |      |        |      |       |       |         |       |

| 3 |     |     |     |       |     |      |      |        |      |       |       |         |       |

| 4 |     |     |     |       |     |      |      |        |      |       |       |         |       |

| 5 |     |     |     |       |     |      |      |        |      |       |       |         |       |

| 6 |     |     |     |       |     |      |      |        |      |       |       |         |       |

Plan:

| 1. |  |

|----|--|

|    |  |

| 3. |  |

|    |  |

| 5. |  |

|    |  |

EEL 3701—Fall 2015 Thursday, 12 November 2015

Page 11/11

## Exam 2

Last Name, First Name

- (8%)

- 7. d) With the present design, you cannot add multiple nibbles (e.g., \$37 + \$5B) because there is no way to remember the carry output between the nibbles. You will fix that issue in this problem. Design a circuit that can be added the existing circuit to "remember" the last carry output (Cout) any time addition has occurred. Call the remembered value R\_Cout. Also design a circuit so that the remembered carry output, R\_Cout, can be used as the carry input (Cin), when a new input LongAdd is true, but use the regular Switch\_Cin switch for the carry input (Cin) when LongAdd is false.