# MODULE 2: ARCHITECTURE OF THE TMS320F28335\*

## Frank Bormann

This work is produced by The Connexions Project and licensed under the Creative Commons Attribution License  $^\dagger$

#### Abstract

An in depth look at the architecture of the TMS320F28335 Microcontroller

## 1 2 Architecture

### **1.1 Introduction**

The TMS320F2833x Digital Signal Controller is capable of executing six basic operations in a single instruction cycle, and therefore the architecture of the device must reflect this feature in some way. Remember this key point when we look into the details of this Digital Signal Controller (DSC). It will help you to understand the 'philosophy' behind the device with its different hardware units. Doing six basic maths operations is no magic; we will find all the hardware modules that are required to do so in this chapter.

In this and other modules, we will discuss the following parts of the architecture:

- Internal bus structure

- CPU

- Direct Memory Access Controller

- Floating-point Arithmetic Unit

- Fixed-point Hardware Multiplier, Arithmetic-Logic-Unit, Hardware-Shifter

- Pipeline Processing of Instructions

- Memory Map

\*Version 1.2: Feb 8, 2011 12:13 pm US/Central †http://creativecommons.org/licenses/by/3.0/

Figure 1

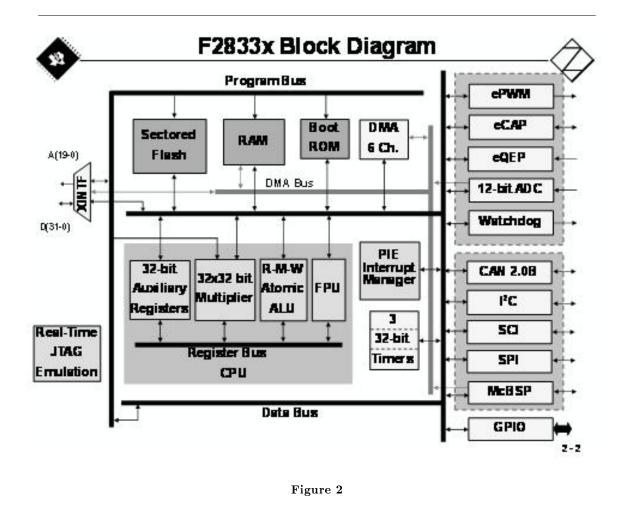

## 1.2 TMS320F2833x Block Diagram

The TMS320F2833x Block Diagram can be divided into the following functional units:

- Internal and external Bus System

- Central Processing Unit (CPU)

- Internal Memory Sections

- Control Peripherals

- Communication Channels

- Direct Memory Access Controller (DMA)

- Interrupt Management Unit (PIE) and Core Time Unit

- Real Time Emulation Interface

#### 1.2.1 Bus System

Since the core of the TMS2833x Microcontroller is a DSP, it can read two operands from memory and transfer them to the central processing unit in a single clock cycle. To do so, the F2833x features two independent bus systems, called the "Program Bus" and the "Data Bus". This type of processor technology is called "Harvard-Architecture". Due to the ability of the F2833x to read operands not only from data memory but also from program memory, Texas Instruments calls its technology a "modified Harvard-Architecture". The "bypass"-arrow in the bottom left corner of Figure 2 indicates this additional feature.

In addition, the F2833x connects all units inside the CPU core to a third bus system, called the "Register Bus", allowing a very fast exchange of data between its parallel mathematical units. Finally, because the DMA unit is able to operate on certain parts of the hardware units independently of the CPU, a "Direct Memory Access Bus" has been added for this purpose.

On the left hand side of Figure 2, you will notice a multiplexer block for data (D31-D0) and address (A19-A0). This is an interface to connect external devices to the F2833x. Please note that you cannot access the external program bus data and the data bus data simultaneously. Compared to a single cycle for internal access to two 32-bit operands, it takes at least 2 cycles to do the same with external memory, not taking

into account additional wait cycles for slower external memories!

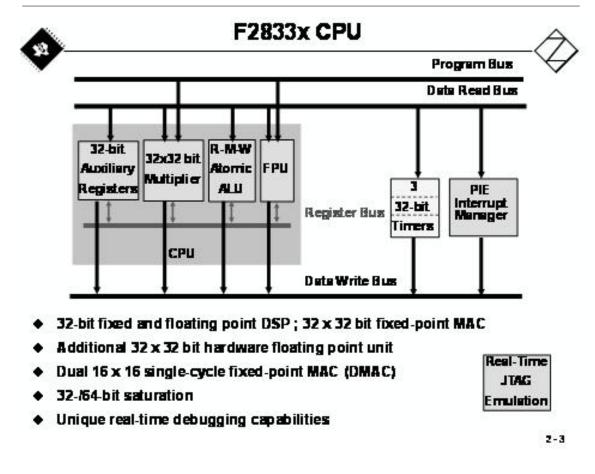

#### 1.2.2 Central Processing Unit (CPU)

The F2833x - CPU is able to execute most of the instructions to perform register-to-register operations and a range of instructions that are commonly used by microcontrollers, e.g. byte packing and unpacking and bit manipulation in a single cycle. The architecture is also supported by powerful addressing modes, which allow the compiler as well as the assembly programmer to generate compact code that corresponds almost one-to-one with the C code.

The F2833x is as efficient in typical math tasks for Digital Signal Processing as it is in the system control tasks that are typically handled by microcontroller devices. This efficiency removes the need for a second processor in many systems.

Three 32-bit timers can be used for general timing purposes or to generate hardware driven time periods for real-time operating systems. The Peripheral Interrupt Expansion Manager (PIE) allows fast interrupt response to the various sources of external and internal signals and events. The PIE-Manager processes individual interrupt vectors for all sources and reduces the response time to an external event, called "Interrupt Latency", to an absolute minimum.

A fixed-point 32-bit by 32-bit hardware multiplier and a 32-bit arithmetic logic unit (ALU) can be used in parallel to simultaneously execute a multiply and an addition operation on fixed-point numbers. The auxiliary register group is equipped with its own arithmetic unit (ARAU)-also used in parallel to perform pointer arithmetic. In addition, a hardware floating-point unit (FPU) for IEEE-754 single point precision numbers allows the direct usage of floating-point numbers from C or MatLab-code.

The JTAG-interface is a very powerful tool to support real-time data exchange between the DSC and a host during the debug phase of project development. A special operating mode called "Real-time Debug" allows variables to be monitored while the code is running in real-time, without a single clock cycle delay in the control code.

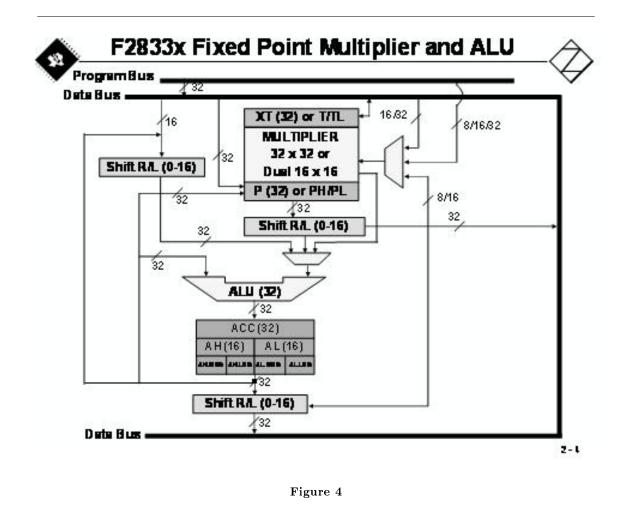

#### 1.2.3 Fixed-point Math Unit

The 32-bit by 32-bit fixed-point "Multiply and Accumulate (MAC)" capabilities of the F2833x and its internal 64-bit processing capabilities enable this DSC to efficiently handle higher numerical resolution problems based on fixed-point numbers. In control applications, a lot of algorithms are numerically based on a technique, called "Binary Fractions", sometimes also called "Integer-Quotient (IQ)"-numbers. The F2833x directly supports this approach. Furthermore, if the samples and coefficients are stored in a binary number of 16 bits or less, which is quite often possible, this controller is able to perform two 16-bit by 16-bit multiply and accumulate instructions simultaneously. The terminology for such an instruction is "Dual Multiply and Accumulate (DMAC)".

Fixed-point multiplication uses the XT ("eXtended Temp") register to hold the first operand and multiply it by a second operand, which is loaded from memory. If XT is loaded from a data memory location and the second operand is fetched from a program memory location, a single-cycle multiply operation can be performed. The result of a multiplication is shifted into the P ("Product") register or directly into the Accumulator (ACC). Remember, if you multiply a 32-bit by a 32-bit number, what size is the result? Answer: 64-bits. The F2833x instruction set includes two groups of multiply operations to store both 32-bit portions of the result into P and ACC. In this way, we can say that the registers ACC and P are combined to form a single 64-bit register.

Three hardware shifters can be used in parallel with other hardware units of the CPU. Shifters are usually used to scale intermediate results in a real-time control loop or just to multiply/divide by numbers of type  $2^{n}$ .

The Arithmetic Logic Unit (ALU) performs all other mathematical operations other than multiplication. The first operand is always the content of the Accumulator (ACC) or a part of it. The second operand for an operation is loaded from data memory, from program memory, from the P register or directly from the multiply unit.

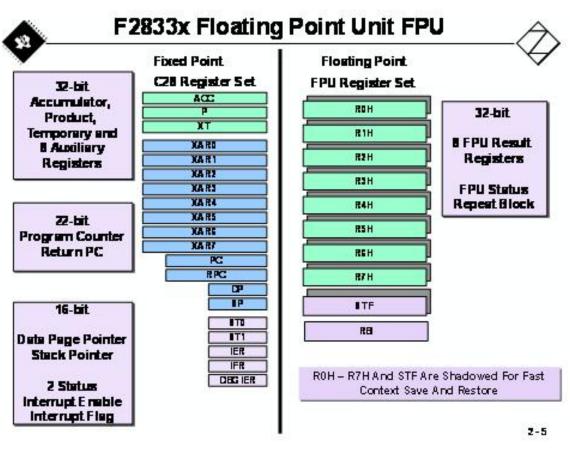

#### 1.2.4 Floating-point Math Unit

To add more flexibility to the device by using single precision floating-point data types in C, Texas Instruments has added a second hardware multiply unit to the F2833x family. The right hand side of Figure 5 shows all the floating-point registers. The 8 general purpose registers (R0H to R7H) are supported by a status register (STF) and a repeat block register (RB). The latter is used to execute a block of machine code without the need for a software loop. Such a technique allows the pipeline of the CPU to run at faster speeds.

The left hand part of Figure 5 shows the fixed-point register set. It consists of the 3 CPU registers, Accumulator (ACC), Product (P) and extended temp (XT), 8 general purpose registers (XAR0...XAR7) and a set of control and status registers, such as "Program Counter" (PC), "Data Page Pointer" (DP), "Stack Pointer" (SP), "Interrupt Enable" (IER), "Interrupt Flag" (IFR) and "Debug Interrupt Enable" (DBGIER).

#### 1.2.5 Data Memory Access

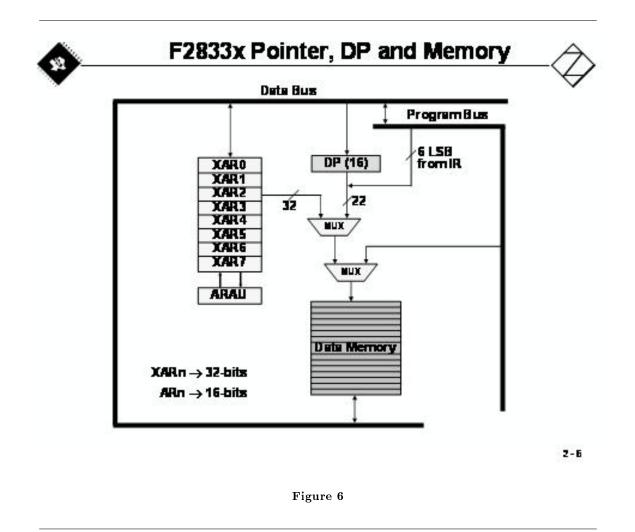

Two basic methods are available to access data memory locations:

- Direct Addressing Mode

- Indirect Addressing Mode

8

Direct addressing mode generates the 22-bit address for a memory access from two sources - a 16-bit register "Data Page (DP)" for the highest 16 bits plus another 6 bits taken from the instruction. Advantage: Once DP is set, we can access any location of the selected page, in any order. Disadvantage: If the code needs to access another page, DP must be changed first.

Indirect addressing mode uses one of eight 32-bit XARn registers to hold the 32-bit address of the operand. Advantage: With the help of the ARAU, pointer arithmetic is available in the same cycle in which an access to a data memory location is made. Disadvantage: A random access to data memory needs the pointer register to be setup with a new value.

The auxiliary register arithmetic unit (ARAU) is able to perform pointer manipulations in the same clock cycle as the access is made to a data memory location. The options for the ARAU are: post-increment, pre-decrement, index addition and subtraction, stack relative operation, circular addressing and bit-reverse addressing with additional options.

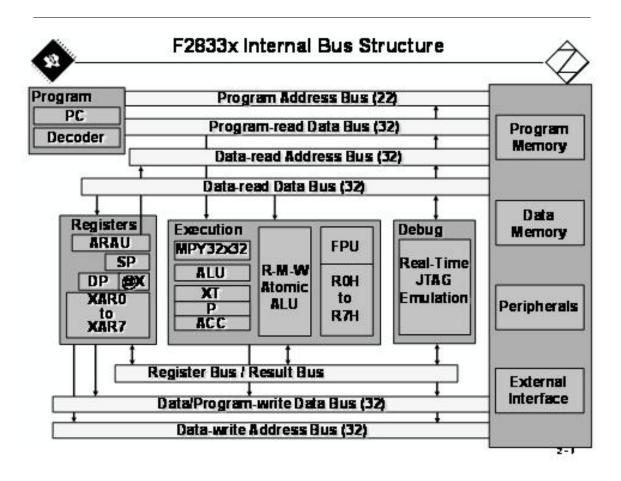

#### 1.2.6 Internal Bus Structure

A typical feature of Digital Signal Processors is their ability to increase the data throughput based on multiple busses. Such busses are used to move data between memory locations, peripheral units and the CPU. The F2833x memory bus architecture contains:

- A program read bus (22-bit address line and 32-bit data line)

- A data read bus (32-bit address line and 32-bit data line)

- A data write bus (32-bit address line and 32-bit data line)

- A register bus (32-bit data line and direct register addressing)

The 32-bit wide data busses allow single cycle 32-bit operations. This multiple bus architecture, known as a Harvard Bus Architecture enables the F2833x to (1) fetch an instruction, (2) read an initial data value and (3) write a second data value, all within in a single clock cycle.

All registers to control peripheral units are mapped into specific locations in data memory space and can be accessed with an ordinary data memory write or read instruction. For important peripheral registers, some security mechanisms are implemented to prevent a modification by accident. All internal memory sections are attached to both program and data memory (called "unified memory model"). It allows the designer to select a certain section to be used as code or as a data section.

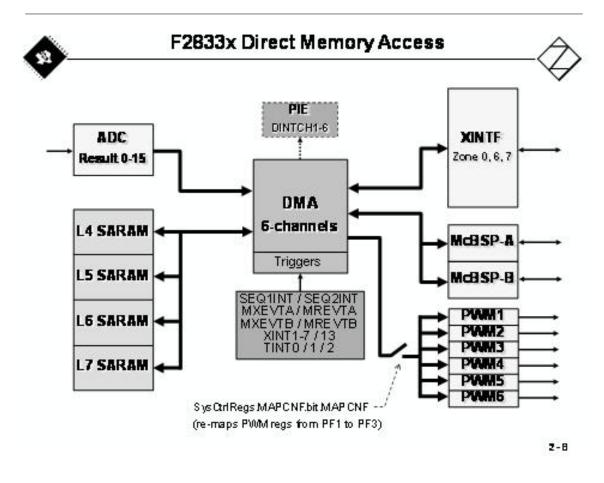

#### 1.2.7 Direct Memory Access Controller (DMA)

A Direct Memory Access Controller has been introduced in the F2833x family. A DMA unit allows a data transfer from a source to a destination unit without the need of an interaction of the CPU. The strength of a digital signal controller (DSC) is measured not only in processor speed, but also in total system capability. As a part of the equation, whenever the CPU bandwidth for a given function can be reduced, the greater the system capability will be. Very often applications spend a significant amount of their bandwidth moving data, whether it is from off-chip memory to on-chip memory or from a peripheral such as an analog-to-digital converter (ADC) to RAM, or even from one peripheral to another. Furthermore, there are times when this data comes in a format that is not compatible with the optimum processing power of the CPU. The DMA module has the ability to free up CPU bandwidth and rearrange the data into a more streamlined processing pattern.

Figure 8

The DMA module is an event-based machine, meaning it requires a peripheral interrupt trigger to start a DMA transfer, such as:

- Analogue to Digital Converter Sequencer 1 (SEQ1INT) or Sequencer 2 (SEQ2INT)

- Multichannel Buffered Serial Port A and B (McBSP-A, McBSP-B) transmit/receive

- External Interrupt Input Signals XINT1-7 and XINT13

- CPU Timers 0, 1 and 2

- Pulse Width Module (PWM) signals ePWM1-6

- Software

As data sources and/or destinations that can be initialized:

- Internal SARAM sections L4 to L7

- All external memory zones XINTF

- ADC result registers (source only)

- McBSP-A and McBSP-B transmit and receive buffers

- PWM units 1-6 (destination only)

## 1.2.8 Atomic Arithmetic Logic Unit (ALU)

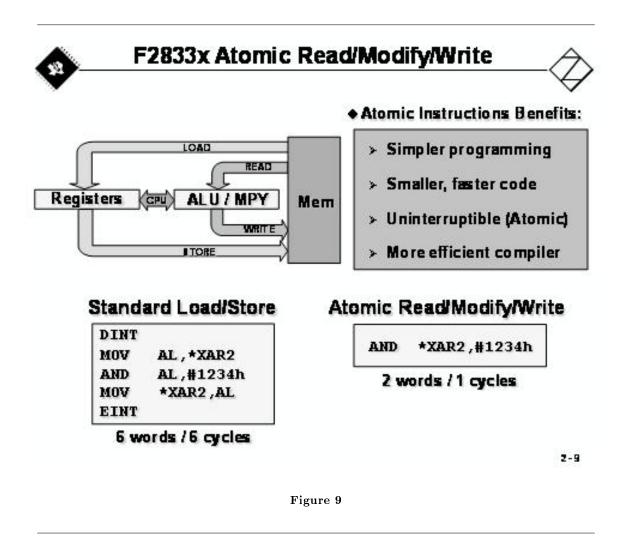

Atomic instructions are common with embedded system controllers. Examples are logical operations, such as AND, OR and EXOR directly performed in data memory locations. Usually, these instructions must be executed without an interruption between read and write accesses; they are called "non-interruptible" or "atomic" instructions. The F2833x atomic Arithmetic Logic Unit (ALU) capability supports such types of instructions; as shown on the right hand side of Figure 9.

By contrast, the traditional coding (left hand side of Figure 9) would execute several cycles slower than atomic instructions.

## **1.3 Instruction Pipeline**

Like almost all today's microprocessors that operate in speed regions above 50 MHz the F2833x also uses a pipeline technique to maximize the code throughput. The F2833x features an 8-stage protected pipeline. The adjective "protected" means that the pipeline unit itself automatically prevents a "write to" and a "read from" from occurring out of sequence at the same location (see instructions E and G in Figure 10). This pipelining also enables the F2833x to execute at high speeds without resorting to expensive highspeed memories. An additional branch-look-ahead hardware minimizes the delay when jumping to another address. Particular assembly instructions called "conditional store operations" avoid pipeline stalls and further improve the overall system performance.

| A                                 | F,                                             | F,                                             | D,                                         | D,                                           | R <sub>1</sub>             | R,  | E  | w  | 1                  |                      | 8-   | st               | age            | e p | ip      | eline                            |

|-----------------------------------|------------------------------------------------|------------------------------------------------|--------------------------------------------|----------------------------------------------|----------------------------|-----|----|----|--------------------|----------------------|------|------------------|----------------|-----|---------|----------------------------------|

| в                                 |                                                | F,                                             | F,                                         | D,                                           | D,                         | R,  | R, | E  | w                  |                      |      |                  |                |     |         |                                  |

| С                                 |                                                |                                                | F,                                         | F,                                           | D,                         | D,  | R, | R, | E                  | w                    | 1    |                  |                |     | 3325.07 | structions                       |

| D                                 |                                                |                                                |                                            | F,                                           | F,                         | D1  | D, | R, | R,                 | E                    | w    |                  |                |     | ·       | E'and 'G'<br>cessisame           |

| Е                                 |                                                |                                                |                                            |                                              | F۱                         | F2  | D, | D, | R,                 | R,                   | E    | w                | T)             | m   |         | ory addre                        |

| F                                 |                                                |                                                |                                            |                                              | _                          | F,  | F, | D, | D,                 | R <sub>1</sub>       | R,   | E                | w              | 1   |         | <i>.</i>                         |

| G                                 |                                                | 100                                            |                                            |                                              |                            |     | F, | F, | D,                 | D,                   | R,   | <b></b>          | R,             | E   | w       | 1                                |

| н                                 |                                                |                                                |                                            |                                              |                            |     |    | F, | F,                 | D,                   | D,   |                  | R <sub>1</sub> | R,  | E       | w                                |

| F2:<br>D1<br>D2<br>R1<br>R2<br>E: | insi<br>Dec<br>Re:<br>Op<br>Gei<br>CPU<br>stor | inuct<br>code<br>colve<br>eran<br>Cope<br>doin | ion<br>Insi<br>Op<br>d Ad<br>eran<br>ng "I | Cont<br>truct<br>eran<br>Idres<br>d<br>real" | tent<br>ion<br>id Ac<br>25 | rkc |    |    | ♦ 0<br>5 0<br>♦ Pi | rder<br>ourc<br>rogr | e co | esu<br>de<br>nec | lits a         |     |         | vritten in<br>wo <b>rry ab</b> o |

Each instruction passes through 8 stages until final completion. Once the pipeline is filled with instructions, one instruction is executed per clock cycle. For a 150MHz device, this equates to 6.67ns per instruction.

Figure 10

The stages are:

- F1: Generate Instruction Address at program bus address lines.

- F2: Read the instruction from program bus data lines.

- D1: Decode Instruction

- D2: Calculate Address information for operand(s) of the instruction

- R1: Load operand(s) address to data and/or program bus address lines

- R2: Read Operand

- X: Execute the instruction

- W: Write back result to data memory

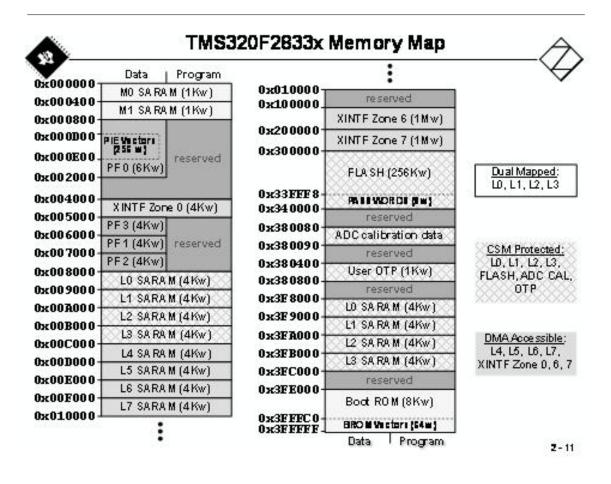

#### 1.4 Memory Map

The memory space of the F2833x is divided into program space and data space. There are several different types of memory available that can be used as both as a program or a data space member. These include independent sections of flash memory, single access RAM (SARAM), one time programmable memory (OTP) and boot ROM. The latter is factory programmed with boot software routines and trigonometric lookup tables used in math based algorithms. Memory space width is always 16 bits.

The F2833x can access memory both on and off the chip. The F2833x uses 32-bit data addresses and 22-bit program addresses. This allows for a total address reach of 4G words (1 word = 16 bits) in data space and 4M words in program space. Memory blocks on all F2833x designs are uniformly mapped to both program and data space.

The memory map above shows the different blocks of memory available to the program and data space.

The non-volatile internal memory consists of a group of FLASH-memory sections, a boot-ROM for up to 12 reset-startup options and a one-time-programmable (OTP) area. FLASH and OTP are usually used to store control code for the application and/or data that must be present at reset. To load information into FLASH and OTP, a dedicated download program is needed, which is also part of the Texas Instruments

Code Composer Studio integrated design environment.

Volatile Memory is split into 10 areas called M0, M1 and L0 - L7 that can be used both as code memory and data memory.

PF0, PF1 and PF2 are Peripheral Frames that cover control and status registers of all peripheral units ("Memory Mapped Registers").

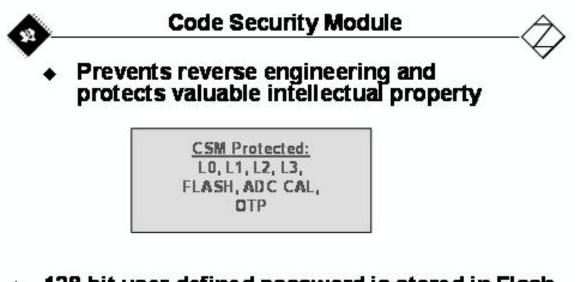

#### 1.5 Code Security Module

There is an internal security module available in all F2833x family members. It is based on a 128-bit password that is written by the *software developer* into the last 8 memory spaces of the internal FLASH (0x3F 7FF8 to 0x3F 7FFF). Once a pattern is written into this area, all further accesses to any of the memory areas covered by this Code Security Module (CSM) are denied, as long as the *user* does not write an identical pattern into password registers of frame PF0.

NOTE: If you write any pattern into the password area by accident, there is no way to get access to this device anymore! Also, any attempt to re-flash a secured device will fail.

So please be careful and do not upset your laboratory technician!

- 128-bit user defined password is stored in Flash

- 128-bits = 2<sup>128</sup> = 3.4 x 10<sup>38</sup> possible passwords

- To try 1 password every 2 cycles at 150 MHz, it would take at least 1.4 x 10<sup>23</sup> years to try all possible combinations!

2-12

Figure 12

The purpose of a password secured device is to prevent reverse engineering of a control system. The code security module will deny any unauthorized access attempts and will protect your intellectual property (IP).

#### **1.6 Interrupt Response**

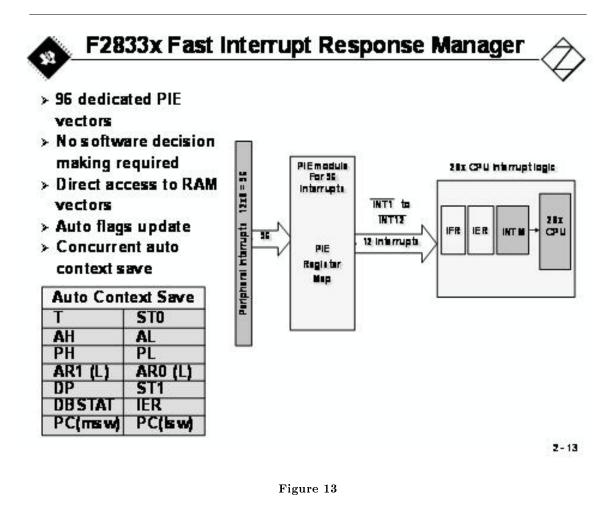

A key feature of a control system is its ability to respond to asynchronous external hardware events as quickly as possible. The F2833x combines such fast interrupt responses with an automatic "context" save of critical CPU registers, which allows for the service of many asynchronous events with minimal latency. Here "context" means all the registers that need to be saved so that you can leave it, carry out some other process, then come back to exactly where you left. F2833x devices implement a zero cycle penalty to save and restore the 14 registers during an interrupt. This feature helps to reduce the interrupt service routine overheads.

We will look in detail into the F2833x interrupt system in Module 6 of this tutorial. The Peripheral Interrupt Expansion (PIE) - Unit allows the user to specify individual interrupt service routines for up to 96 internal and external interrupt events. All possible 96 interrupt sources share 14 maskable interrupt lines (INT1 to INT14), 12 of which are controlled by the PIE - module.

16

The auto context save loads 14 important CPU registers, as shown in Figure 13 above, into a stack memory, which is pointed to by a stack pointer (SP) register. The stack is part of the data memory and must reside in the lower 64K words of data memory.

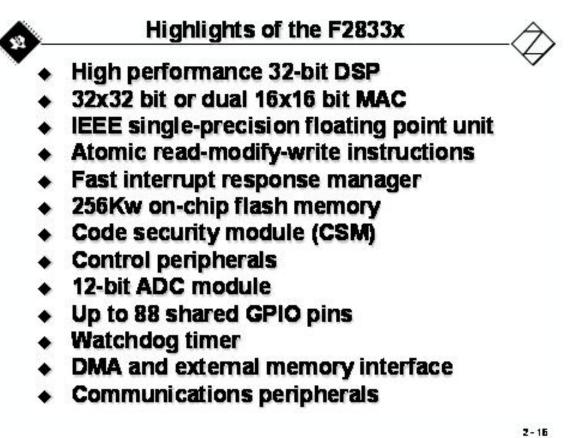

## 1.7 Operating Modes

The F2833x is a member of the TMS320C2000 family of Digital Signal Controllers (DSCs). This family consists both of 32-bit fixed-point and floating-point devices and also of 16-bit members. The Test Mode is used for fabrication test purposes only. The F2833x can be switched from its native mode into an operating mode, that is source code compatible with the 16-bit group C24x/C240x. Code, which has been previously written for a C24x device, can be reassembled to run on a F2833x device. This allows for migration of existing code onto the F2833x.

| ~ | F2833x Operating Modes | $\wedge$   |

|---|------------------------|------------|

| V |                        | $-\forall$ |

|   |                        |            |

| Mode Type            | Mode<br>OBJMODE |   | Compiler Option |  |  |

|----------------------|-----------------|---|-----------------|--|--|

| C28x Native Mode     | 1               | 0 | -v28            |  |  |

| C24x Compatible Mode | 1               | 1 | -v28 –m20       |  |  |

| Test Mode (default)  | 0               | 0 |                 |  |  |

| Reserved             | 0               | 1 |                 |  |  |

- Almost all us es will run in C28x Native Mode

- The bootloader will automatically select C28x Native Mode after reset

- C24x compatible mode is mostly for backwards compatibility with an older processor family

2-14

#### Figure 14

In fact, the F2833x silicon is able to operate in three different modes:

- C28x Mode: takes advantage of all 32-bit features of the F2833x device

- C24x Mode: source code compatibility to the 16-bit family members

• Test – Mode: intermediate operating mode, test purposes only.

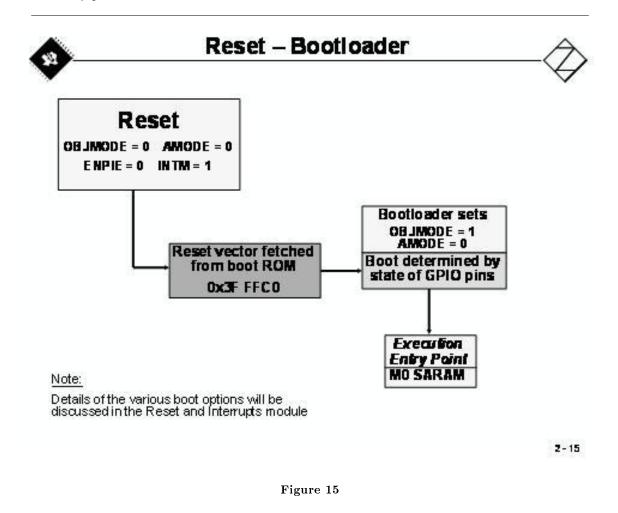

After RESET, the device is set into test mode. To take advantage of the full computing power of an F2833x device, set the control flag "OBJMODE" to 1 which will switch the device into F2833x native mode. If you start the execution of your code from the boot code entry point, the boot code will set that bit for you.

#### 1.8 Reset Behaviour

After a valid RESET-signal is applied to the F2833x, the following sequence depends on some external pins on this DSC.

An active RESET signal will read the first address to be loaded into the Program Counter register (PC) from address 0x3F FFC0, which is in boot memory. The value inside this address is the address of the beginning of the boot code sequence. As a result, the F2833x jumps directly to the *internal boot code* memory. This code has been developed by TI to be able to distinguish between 12 different start options for the F2833x. The active option is derived from the status of 4 general-purpose input pins (GPIO) at this very moment. For our tutorial we use the volatile memory M0 as code memory and its first address as the execution entry point.

1.9 Summary of TMS320F2833x Architecture

Figure 16