## TMS320C28x CPU and Instruction Set Reference Guide

Literature Number: SPRU430E August 2001 – Revised January 2009

### **Preface**

### **Read This First**

### About This Manual

This manual describes the central processing unit (CPU) and the assembly language instructions of the TMS320C28x 32-bit fixed-point CPU. It also describes emulation features available on these devices. A summary of the chapters and appendixes follows:

### Chapter 1 Architectural Overview

This chapter introduces the C2800 CPU that is at the heart of each TMS320C28x device. The chapter includes a memory map and a high-level description of the memory interface that connects the core with memory and peripheral devices.

### Chapter 2 Central Processing Unit

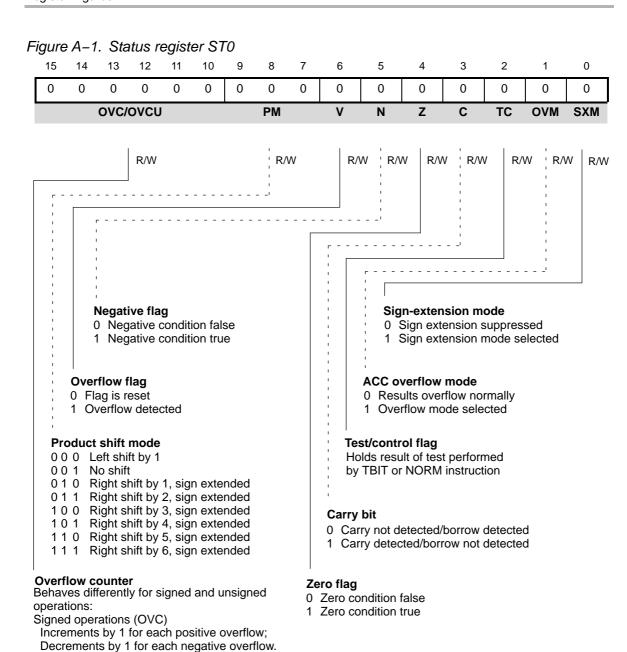

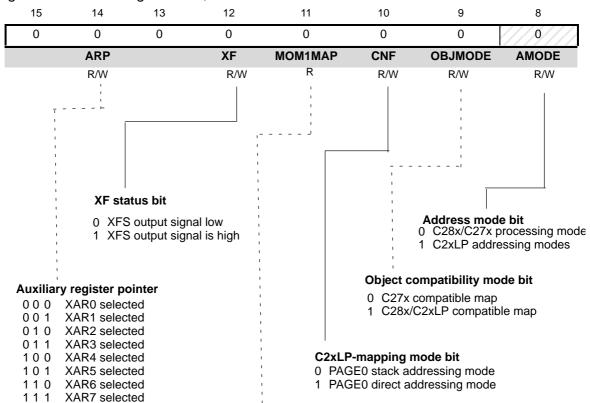

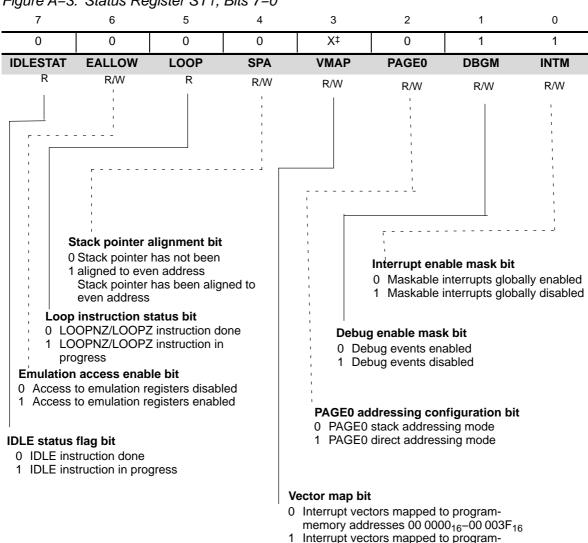

This chapter describes the architecture, registers, and primary functions of the CPU. The chapter includes detailed descriptions of the flag and control bits in the most important CPU registers, status registers ST0 and ST1.

### Chapter 3 Interrupts and Reset

This chapter describes the interrupts and how they are handled by the CPU. The chapter also explains the effects of a reset on the CPU and includes discussion of the automatic context save performed by the CPU prior to servicing an interrupt.

### Chapter 4 Pipeline

This chapter describes the phases and operation of the instruction pipeline. The chapter is primarily for readers interested in increasing the efficiency of their programs by preventing pipeline delays.

### Chapter 5 Addressing Modes

This chapter explains the modes by which the assembly language instructions accept data and access register and memory locations. The chapter includes a description of how addressing-mode information is encoded in opcodes.

### Chapter 6 Assembly Language Instructions

This chapter provides summaries of the instruction set and detailed descriptions (including examples) for the instructions. The chapter includes an explanation of how 32-bit accesses are aligned to even addresses.

### **Chapter 7** Emulation Features

This chapter describes the TMS320C28x emulation features that can be used with only a JTAG port and two additional emulation pins.

### Appendix A Register Quick Reference

This appendix is a concise central resource for information about the status and control registers of the CPU. The chapter includes figures that summarize the bit fields of the registers.

### Appendix B C2xLP and C28x Architectural Differences

This appendix describes the differences in the architecture of the C2xLP and the C28x.

### Appendix C Migration From C2xLP

This appendix explains how to migrate code from the C2xLP to the C28x.

### Appendix D C2xLP Instruction Set Compatibility

This appendix describes the instruction set compatibility with the C2xLP.

### Appendix E Migration From C27x to C28x

This appendix explains how to migrate code from the C27x to the C28x.

### Appendix G Glossary

This appendix explains abbreviations, acronyms, and special terminology used throughout this document.

### **Notational Conventions**

| This  | document | uses | the | following | conventions: |

|-------|----------|------|-----|-----------|--------------|

| 11113 | accument | uses | uic | TOHOWING  | CONVENIENCE. |

MOVB AR0, #40h

| 1011 | Tollowing conventions.                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|      | The device number TMS320C28x is very often abbreviated as '28x.                                                                                                                                                                                                                                                                       |  |  |  |  |

|      | Program examples are shown in a ${\tt special}\ {\tt typeface}.$ Here is a sample line of program code:                                                                                                                                                                                                                               |  |  |  |  |

|      | PUSH IER                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|      | Portions of an instruction syntax that are in <b>bold</b> should be entered as shown; portions of a syntax that are in <i>italics</i> are variables indicating information that should be entered. Here is an example of an instruction syntax:                                                                                       |  |  |  |  |

|      | MOV ARx, *-SP[6bif]                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|      | MOV is the instruction mnemonic. This instruction has two operands, indicated by $\mathbf{AR}x$ and *- $\mathbf{SP}[6bit]$ . Where the variable $x$ appears, you type a value from 0 to 5; where the $6bit$ appears, you type a 6-bit constant. The rest of the instruction, including the square brackets, must be entered as shown. |  |  |  |  |

|      | When braces or brackets enclose an operand, as in {operand}, the operand is optional. If you use an optional operand, you specify the information within the braces; you do not enter the braces themselves. In the following syntax, the operand << shift is optional:                                                               |  |  |  |  |

|      | MOV ACC, *-SP[6bit] {<< shift }                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|      | MOV ACC, *-SP{6bit} {<< shift}                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|      | For example, you could use either of the following instructions:                                                                                                                                                                                                                                                                      |  |  |  |  |

|      | MOV ACC, *-SP[5]                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|      | MOV ACC, *-SP[5]<< 4                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|      | In most cases, hexadecimal numbers are shown with a subscript of 16. For example, the hexadecimal number 40 would be shown as $40_{16}$ . An exception to this rule is a hexadecimal number in a code example; these hexadecimal numbers have the suffix h. For example, the number 40 in the following code is a hexadecimal 40.     |  |  |  |  |

Similarly, binary numbers usually are shown with a subscript of 2. For example, the binary number 4 would be shown as 0100<sub>2</sub>. Binary numbers in example code have the suffix b. For example, the following code uses a binary 4.

MOVB AR0, #0100b

Bus signals and bits are sometimes represented with the following notations:

| Notation      | Description                  | Example                                                                   |

|---------------|------------------------------|---------------------------------------------------------------------------|

| Bus(n:m)      | Signals n through m of bus   | PRDB(31:0) represents the 32 signals of the program-read data bus (PRDB). |

| Register(n:m) | Bits n through m of register | T(3:0) represents the 4 least significant bits of the T register.         |

| Register(n)   | Bit n of register            | IER(4) represents bit 4 of the interrupt enable register (IER).           |

☐ Concatenated values are represented with the following notation:

| Notation | Description           | Example                                                                                                               |

|----------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|

| x:y      | x concatenated with y | AR1:AR0 is the concatenation of<br>the 16-bit registers AR1 and<br>AR0. AR0 is the low word. AR1<br>is the high word. |

☐ If a signal is from an active-low pin, the name of the signal is qualified with an overbar (for example, INT1). If a signal is from an active-high pin or from hardware inside the the device (in which case, the polarity is irrelevant), the name of the signal is left unqualified (for example, DLOGINT).

#### Related Documentation From Texas Instruments

The following books describe the TMS320C28x DSP and related support tools. The documents are available for downloading on the Texas Instruments website (www.ti.com).

- TMS320F2801, TMS320F2806, TMS320F2808 Digital Signal Processors (literature number SPRS230) data sheet contains the pinout, signal descriptions, as well as electrical and timing specifications for the F280x devices.

- TMS320C28x Assembly Language Tools User's Guide (literature number SPRU513) describes the assembly language tools (assembler and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for the TMS320C28x<sup>™</sup> device.

- TMS320C28x Optimizing C Compiler User's Guide (literature number SPRU514) describes the TMS320C28x<sup>™</sup> C/C++ compiler. This compiler accepts ANSI standard C/C++ source code and produces TMS320<sup>™</sup> DSP assembly language source code for the TMS320C28x device.

- TMS320F2810, TMS320F2811, TMS320F2812, TMS320C2810, TMS320C2811, and TMS320C2812 Digital Signal Processors (literature number SPRS174) data sheet contains the electrical and timing specifications for these devices, as well as signal descriptions and pinouts for all of the available packages.

- TMS320x28xx, 28xxx DSP Peripherals Reference Guide (literature number SPRU566) describes all the peripherals available for TMS320x28xx and TMS320x28xxx devices.

- TMS320C28x Floating Point Unit and Instruction Set Reference Guide (literature number SPRUEO2) describes the CPU architecture, pipeline, instruction set, and interrupts of the C28x floating–point DSP.

### **Trademarks**

320 Hotline On-line is a trademark of Texas Instruments Incorporated.

HP-UX is a trademark of Hewlett-Packard Company.

IBM and PC are trademarks of International Business Machines Corporation.

Intel is a trademark of Intel Corporation.

MS-DOS is a registered trademark of Microsoft Corporation.

PAL® is a registered trademark of Advanced Micro Devices, Inc.

SunOS is a trademark of Sun Microsystems, Inc.

C2xLP, C27x, C28x, TMS320C28x, TMS320F28x, and XDS510 are trademarks of Texas Instruments Incorporated.

# **Contents**

|   | Archi | itootura  | l Overview                                                            | 1_1  |

|---|-------|-----------|-----------------------------------------------------------------------|------|

| • |       |           | e architecture and memory map of the T320C28x DSP CPU.                |      |

|   | 1.1   |           | action to the CPU                                                     | 1-2  |

|   |       | 1.1.1     | Compatibility With Other TMS320 CPUs                                  |      |

|   |       | 1.1.2     | Switching to C28x Mode From Reset                                     |      |

|   | 1.2   |           | onents of the CPU                                                     |      |

|   |       | 1.2.1     | Central Processing Unit (CPU)                                         |      |

|   |       | 1.2.2     | Emulation Logic                                                       |      |

|   |       | 1.2.3     | Signals                                                               |      |

|   | 1.3   | Memor     | y Map                                                                 | 1-7  |

|   |       | 1.3.1     | CPU Interrupt Vectors                                                 | 1-7  |

|   | 1.4   | Memor     | y Interface                                                           | 1-9  |

|   |       | 1.4.1     | Address and Data Buses                                                | 1-9  |

|   |       | 1.4.2     | Special Bus Operations                                                |      |

|   |       | 1.4.3     | Alignment of 32-Bit Accesses to Even Addresses                        | 1-11 |

| 2 | Centi | ral Proc  | essing Unit                                                           | 2-1  |

|   | Desc  | ribes the | architecture, registers, and primary functions of the TMS320C28x CPU. |      |

|   | 2.1   | CPU A     | rchitecture                                                           | 2-2  |

|   | 2.2   |           | egisters                                                              |      |

|   |       | 2.2.1     | Accumulator (ACC, AH, AL)                                             | 2-6  |

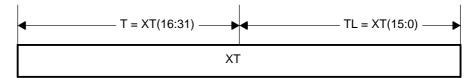

|   |       | 2.2.2     | Multiplicand Register (XT)                                            |      |

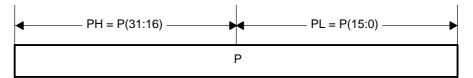

|   |       | 2.2.3     | Product Register (P, PH, PL)                                          | 2-9  |

|   |       | 2.2.4     | Data Page Pointer (DP)                                                | 2-10 |

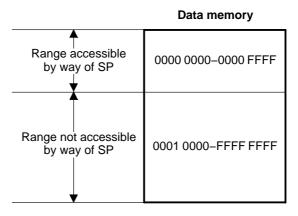

|   |       | 2.2.5     | Stack Pointer (SP)                                                    | 2-11 |

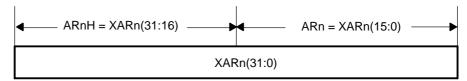

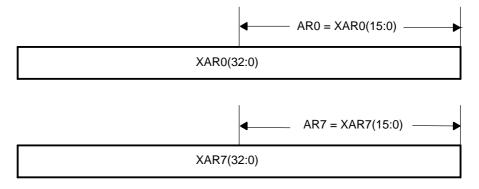

|   |       | 2.2.6     | Auxiliary Registers (XAR0–XAR7, AR0–AR7)                              | 2-12 |

|   |       | 2.2.7     | Program Counter (PC)                                                  |      |

|   |       | 2.2.8     | Return Program Counter (RPC)                                          |      |

|   |       | 2.2.9     | Status Registers (ST0, ST1)                                           |      |

|   |       | 2.2.10    | 1 , , ,                                                               |      |

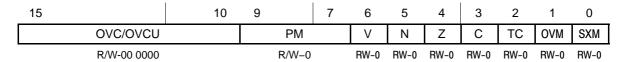

|   | 2.3   |           | Register (ST0)                                                        |      |

|   | 2.4   |           | Register ST1                                                          |      |

|   | 2.5   | •         | m Flow                                                                |      |

|   |       | 2.5.1     | Interrupts                                                            |      |

|   |       | 2.5.2     | Branches, Calls, and Returns                                          | 2-39 |

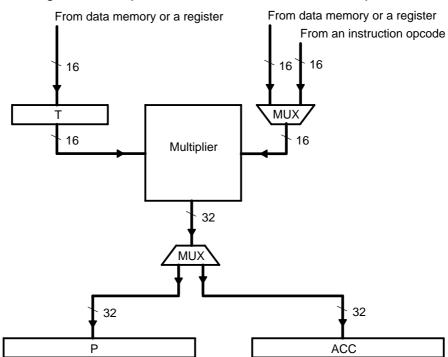

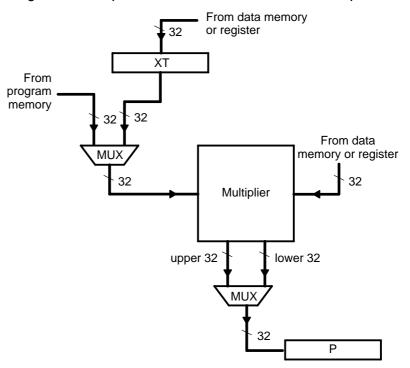

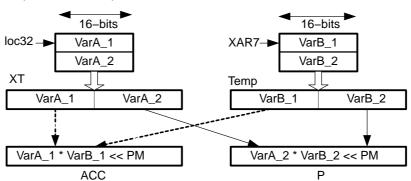

|   | 2.6   | 2.6.1<br>2.6.2 | Repeating a Single Instruction Instruction Pipeline y Operations 16-bit X 16-bit Multiplication 32-Bit X 32-Bit Multiplication perations | 2-40<br>2-41<br>2-41<br>2-42 |

|---|-------|----------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|   |       |                |                                                                                                                                          |                              |

| 3 | Desci | ribes the      | ots and Reset<br>TMS320C28x interrupts and how they are handled by the CPU. Also explain<br>a hardware reset.                            |                              |

|   | 3.1   | CPU In         | nterrupts Overview                                                                                                                       | 3-2                          |

|   | 3.2   | CPU In         | sterrupt Vectors and Priorities                                                                                                          | 3-4                          |

|   | 3.3   | Maskal         | ble Interrupts: INT1-INT14, DLOGINT, and RTOSINT                                                                                         | 3-6                          |

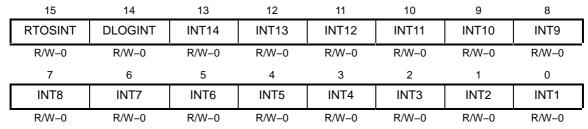

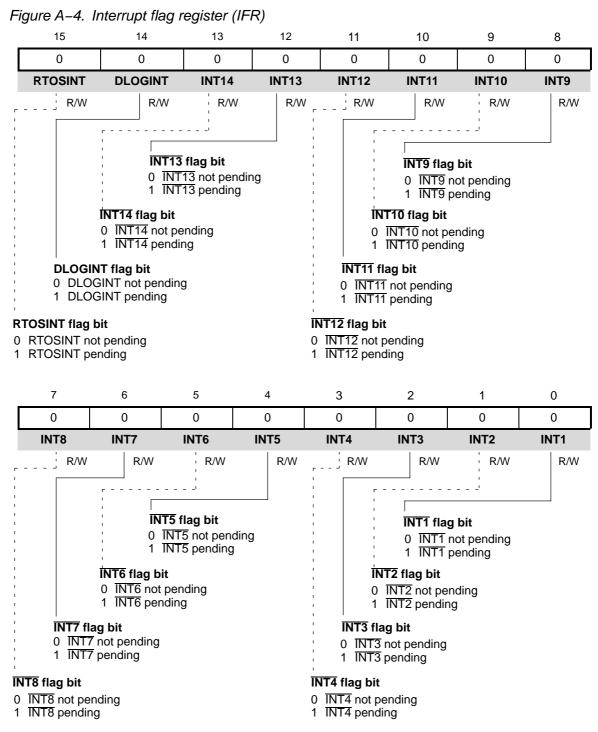

|   |       | 3.3.1          | CPU Interrupt Flag Register (IFR)                                                                                                        | 3-7                          |

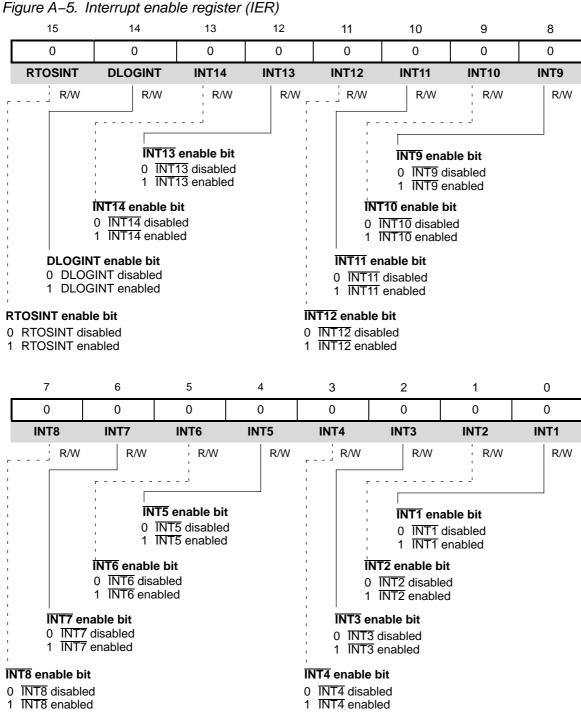

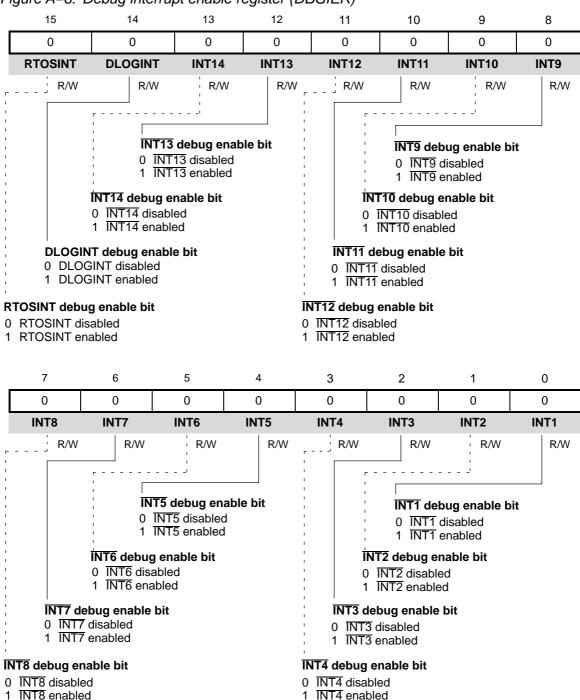

|   |       | 3.3.2          | CPU Interrupt Enable Register (IER) and CPU Debug Interrupt Enable Register (DBGIER)                                                     | 3-8                          |

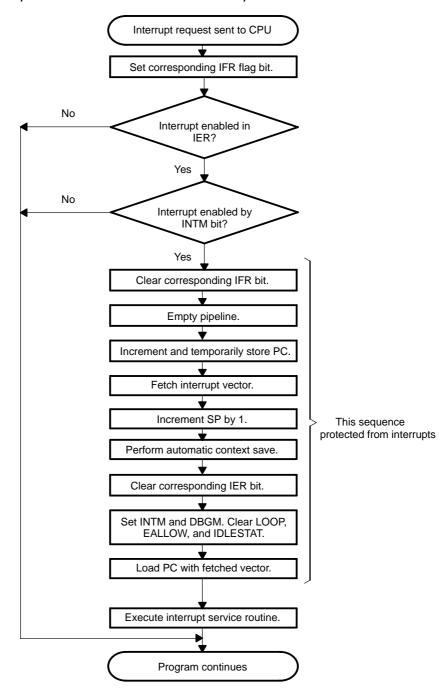

|   | 3.4   | Standa         | ard Operation for Maskable Interrupts                                                                                                    |                              |

|   | 3.5   |                | skable Interrupts                                                                                                                        |                              |

|   |       | 3.5.1          | INTR Instruction                                                                                                                         | 3-17                         |

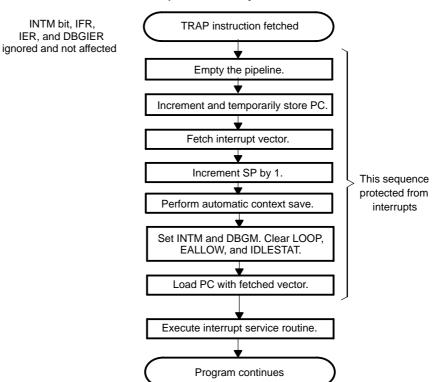

|   |       | 3.5.2          | TRAP Instruction                                                                                                                         | 3-18                         |

|   |       | 3.5.3          | Hardware Interrupt NMI                                                                                                                   | 3-21                         |

|   | 3.6   | Illegal-l      | Instruction Trap                                                                                                                         | 3-22                         |

|   | 3.7   | Hardwa         | are Reset (RS)                                                                                                                           | 3-23                         |

| 4 | Pipel | ine            |                                                                                                                                          | 4-1                          |

| - |       |                | phases and operation of the instruction pipeline.                                                                                        |                              |

|   | 4.1   |                | ing of Instructions                                                                                                                      | 4-2                          |

|   |       | 4.1.1          | Decoupled Pipeline Segments                                                                                                              |                              |

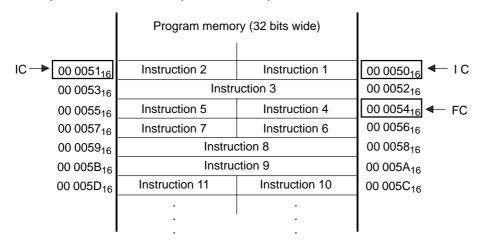

|   |       | 4.1.2          | Instruction-Fetch Mechanism                                                                                                              |                              |

|   |       | 4.1.3          | Address Counters FC, IC, and PC                                                                                                          |                              |

|   | 4.2   | Visualiz       | zing Pipeline Activity                                                                                                                   |                              |

|   | 4.3   |                | s in Pipeline Activity                                                                                                                   |                              |

|   |       | 4.3.1          | Wait States                                                                                                                              | 4-10                         |

|   |       | 4.3.2          | Instruction-Not-Available Condition                                                                                                      | 4-10                         |

|   | 4.4   | Pipelin        | e Protection                                                                                                                             | 4-12                         |

|   |       | 4.4.1          | Protection During Reads and Writes to the Same Data-Space Location                                                                       | 4-12                         |

|   |       | 4.4.2          | Protection Against Register Conflicts                                                                                                    | 4-13                         |

|   | 4.5   | Avoidir        | ng Unprotected Operations                                                                                                                | 4-16                         |

|   |       | 4.5.1          | Unprotected Program-Space Reads and Writes                                                                                               | 4-16                         |

|   |       | 4.5.2          | An Access to One Location That Affects Another Location                                                                                  |                              |

|   |       | 4.5.3          | Write Followed By Read Protection Mode                                                                                                   | 4-17                         |

| 5 | C28x | Addressing Modes                                                                                                                                | 5-1    |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|   | Desc | ribes the addressing modes of the C28x.                                                                                                         |        |

|   | 5.1  | Types of Addressing Modes                                                                                                                       | 5-2    |

|   | 5.2  | Addressing Modes Select Bit (AMODE)                                                                                                             |        |

|   | 5.3  | Assembler/Compiler Tracking of AMODE Bit                                                                                                        |        |

|   | 5.4  | Direct Addressing Modes (DP)                                                                                                                    |        |

|   | 5.5  | Stack Addressing Modes (SP)                                                                                                                     |        |

|   | 5.6  | Indirect Addressing Modes                                                                                                                       |        |

|   |      | 5.6.1 C28x Indirect Addressing Modes (XAR0 to XAR7)                                                                                             |        |

|   |      | 5.6.2 C2xLP Indirect Addressing Modes (ARP, XAR0 to XAR7)                                                                                       |        |

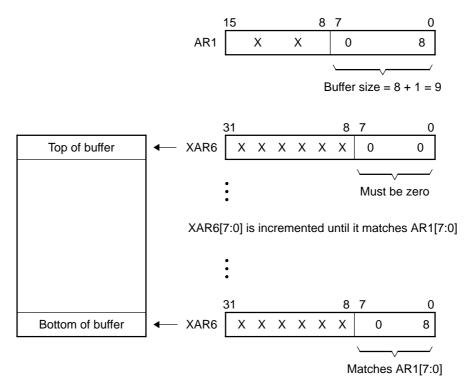

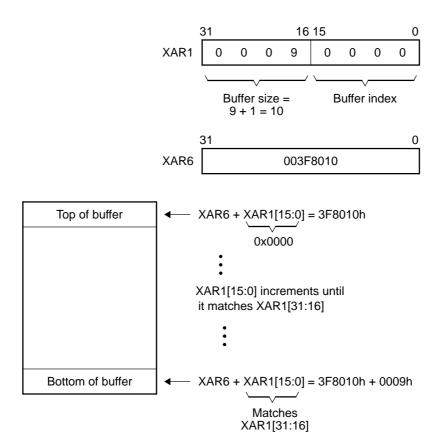

|   |      | 5.6.3 Circular Indirect Addressing Modes (XAR6, XAR1)                                                                                           |        |

|   | 5.7  | Register Addressing Modes                                                                                                                       |        |

|   |      | 5.7.1 32-Bit Register Addressing Modes                                                                                                          |        |

|   |      | 5.7.2 16-Bit Register Addressing Modes                                                                                                          |        |

|   | 5.8  | Data/Program/IO Space Immediate Addressing Modes                                                                                                |        |

|   | 5.9  | Program Space Indirect Addressing Modes                                                                                                         |        |

|   | 5.10 | Byte Addressing Modes                                                                                                                           |        |

|   | 5.11 | Alignment of 32-Bit Operations                                                                                                                  |        |

|   |      |                                                                                                                                                 |        |

|   |      | ents summaries of the instruction set, defines special symbols and notations used, a<br>ribes each instruction in detail in alphabetical order. |        |

|   | 6.1  | Instruction Set Summary (Organized by Function)                                                                                                 |        |

|   | 6.2  | Register Operations                                                                                                                             | 6-4    |

| 7 | Emul | lation Features                                                                                                                                 | 7-1    |

| • |      | ains features supported by the TC2800 CPU for testing and debugging programs.                                                                   |        |

|   | 7.1  | Overview of Emulation Features                                                                                                                  | 7-2    |

|   | 7.2  | Debug Interface                                                                                                                                 |        |

|   | 7.3  | Debug Terminology                                                                                                                               |        |

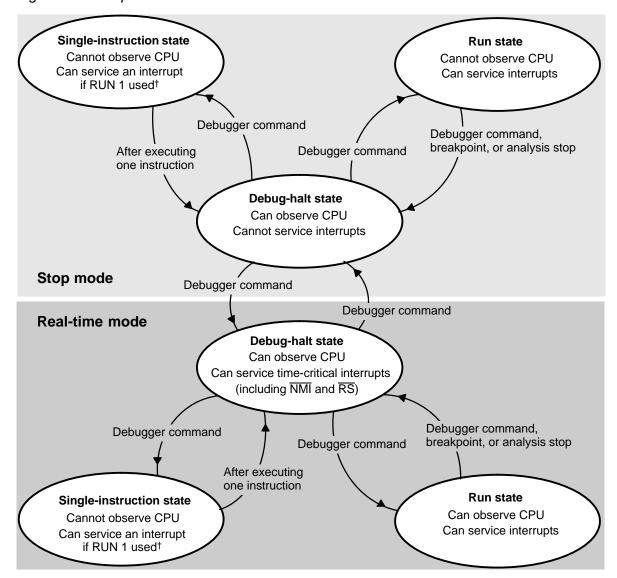

|   | 7.4  | Execution Control Modes                                                                                                                         |        |

|   |      | 7.4.1 Stop Mode                                                                                                                                 |        |

|   |      | 7.4.2 Real-Time Mode                                                                                                                            |        |

|   |      | Caution about breakpoints within time-critical interrupt service routines                                                                       |        |

|   |      | 7.4.3 Summary of Stop Mode and Real-Time Mode                                                                                                   |        |

|   | 7.5  | Aborting Interrupts With the ABORTI Instruction                                                                                                 |        |

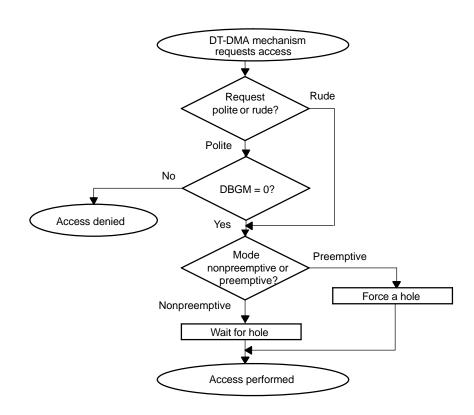

|   | 7.6  | DT-DMA Mechanism                                                                                                                                |        |

|   | 7.7  | Analysis Breakpoints, Watchpoints, and Counter(s)                                                                                               |        |

|   |      | 7.7.1 Analysis Breakpoints                                                                                                                      |        |

|   |      | 7.7.2 Watchpoints                                                                                                                               |        |

|   |      | 7.7.3 Benchmark Counter/Event Counter(s)                                                                                                        |        |

|   |      | 7.7.4 Typical Analysis Unit Configurations                                                                                                      | . 7-21 |

|   | 7.8   | Data Logging                                                                                      | 7-23       |

|---|-------|---------------------------------------------------------------------------------------------------|------------|

|   |       | 7.8.1 Creating a Data Logging Transfer Buffer                                                     | 7-23       |

|   |       | 7.8.2 Accessing the Emulation Registers Properly                                                  | 7-26       |

|   |       | 7.8.3 Data Log Interrupt (DLOGINT)                                                                | 7-27       |

|   |       | 7.8.4 Examples of Data Logging                                                                    | 7-28       |

|   | 7.9   | Sharing Analysis Resources                                                                        | 7-30       |

|   | 7.10  | Diagnostics and Recovery                                                                          | 7-31       |

| Α | Regis | ster Quick Reference                                                                              | A-1        |

|   |       | concise, central resource for information about the status and control registe 320C28x CPU.       | ers of the |

|   | A.1   | Reset Values of and Instructions for Accessing the Registers                                      |            |

|   | A.2   | Register Figures                                                                                  | A-3        |

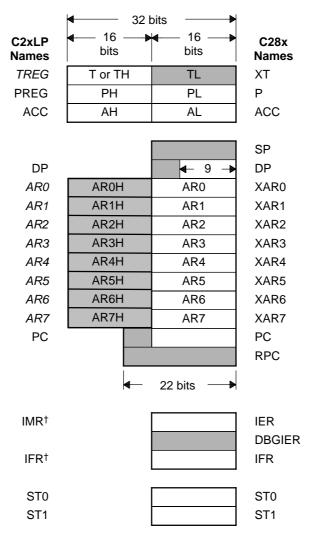

| В |       | P and C28x Architectural Differences                                                              |            |

|   | •     | ights some the architectural differences between C2xLP and C28x, with a focus<br>and memory maps. | on regis-  |

|   | FB.1  | Summary of Architecture Differences Between C2xLP and C28x                                        |            |

|   |       | B.1.1 Enhancements of the C28x over the C2xLP:                                                    |            |

|   | B.2   | Registers                                                                                         |            |

|   |       | B.2.1 CPU Register Changes                                                                        |            |

|   |       | B.2.2 Data Page (DP) Pointer Changes                                                              |            |

|   |       | B.2.3 Status Register Changes                                                                     |            |

|   |       | B.2.4 Register Reset Conditions                                                                   |            |

|   | B.3   | Memory Map                                                                                        | B-12       |

| С | C2xL  | P Migration Guidelines                                                                            | C-1        |

|   | Provi | des guidelines for C2xLP code migration to a C28x device.                                         |            |

|   | C.1   | Introduction                                                                                      | C-2        |

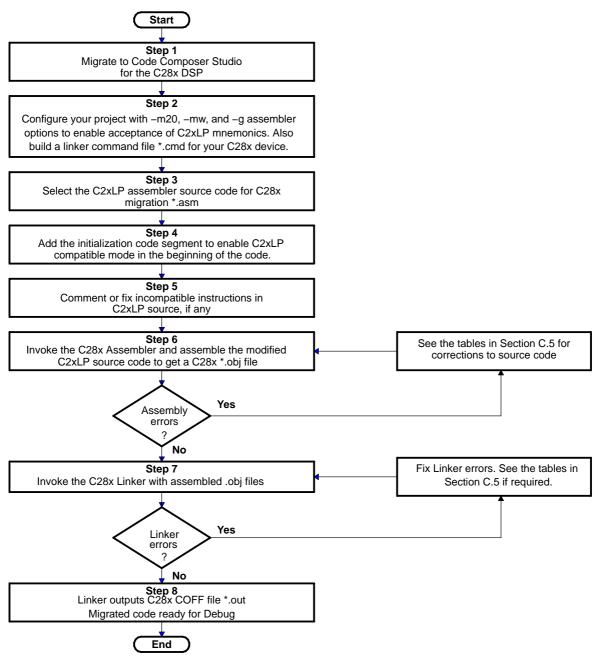

|   | C.2   | Recommended Migration Flow                                                                        | C-3        |

|   | C.3   | Mixing C2xLP and C28x Assembly                                                                    | C-6        |

|   | C.4   | Code Examples                                                                                     | C-7        |

|   |       | C.4.1 Boot Code for C28x operating mode initalization                                             | C-7        |

|   |       | C.4.2 IER/IFR Code                                                                                | C-7        |

|   |       | C.4.3 Context Save/Restore                                                                        | C-8        |

|   | C.5   | Reference Tables for C2xLP Code Migration Topics                                                  | C-10       |

| D | C2xL  | P Instruction Set Compatibility                                                                   | D-1        |

|   | Desc  | ribes the instruction set compatibility between the C2xLP and the C28x.                           |            |

|   | D.1   | Condition Tests on Flags                                                                          | D-2        |

|   | D.2   | C2xLP vs. C28x Mnemonics                                                                          | D-3        |

|   | DЗ    | Reneatable Instructions                                                                           | D-0        |

| Ε | Migra | ation Fr | om C27x to C28x                                                                   | E-1              |

|---|-------|----------|-----------------------------------------------------------------------------------|------------------|

|   | _     | _        | e architectural differences between C27x and C28x and describe<br>om C27x to C28x | s how to migrate |

|   | E.1   | Archite  | ecture Changes                                                                    | E-2              |

|   |       | E.1.1    | Changes to Registers                                                              | E-2              |

|   |       | E.1.2    | Full Context Save and Restore                                                     | E-5              |

|   |       | E.1.3    | B0/B1 Memory Map Consideration                                                    | E-6              |

|   |       | E.1.4    | C27x Object Compatibility                                                         | E-8              |

|   | E.2   | Moving   | g to a C28x Object                                                                | E-9              |

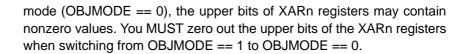

|   |       | E.2.1    | Caution When Changing OJBMODE                                                     | E-9              |

|   | E.3   |          | ing to C28x Object Code                                                           |                  |

|   |       | E.3.1    | Instruction Syntax Changes                                                        | E-11             |

|   |       | E.3.2    | Repeatable Instructions                                                           | E-13             |

|   |       | E.3.3    | Changes to the SUBCU Instruction                                                  | E-14             |

|   | E.4   |          | iling C28x Source Code                                                            |                  |

| F | Gloss | sarv     |                                                                                   | G-1              |

# **Figures**

| 1–1  | High-Level Conceptual Diagram of the CPU                                 | 1-4  |

|------|--------------------------------------------------------------------------|------|

| 1–2  | TMS320C28x High-Level Memory Map                                         |      |

| 2–1  | Conceptual Block Diagram of the CPU                                      |      |

| 2–2  | C28x Registers                                                           |      |

| 2–3  | Individually Accessible Portions of the Accumulator                      |      |

| 2–4  | Individually Accessible Halves of the XT Register                        |      |

| 2–5  | Individually Accessible Halves of the P Register                         | 2-9  |

| 2–6  | Pages of Data Memory                                                     | 2-11 |

| 2–7  | Address Reach of the Stack Pointer                                       |      |

| 2–8  | XAR0 – XAR7 Registers                                                    | 2-13 |

| 2–9  | XAR0 – XAR7                                                              |      |

| 2–10 | Bit Fields of Status Register (ST0)                                      | 2-16 |

| 2–11 | Bit Fields of Status Register 1 (ST1)                                    |      |

| 2–12 | Conceptual Diagram of Components Involved in 16 X16-Bit Multiplication   | 2-42 |

| 2–13 | Conceptual Diagram of Components Involved in 32 X 32-Bit Multiplication  | 2-43 |

| 3–1  | Interrupt Flag Register (IFR)                                            | 3-7  |

| 3–2  | Interrupt Enable Register (IER)                                          | 3-9  |

| 3–3  | Debug Interrupt Enable Register (DBGIER)                                 | 3-10 |

| 3–4  | Standard Operation for CPU Maskable Interrupts                           | 3-12 |

| 3–5  | Functional Flow Chart for an Interrupt Initiated by the TRAP Instruction | 3-18 |

| 5–1  | Circular Buffer with AMODE = 0                                           | 5-22 |

| 5–2  | Circular Buffer with AMODE = 1                                           | 5-24 |

| 7–1  | JTAG Header to Interface a Target to the Scan Controller                 | 7-3  |

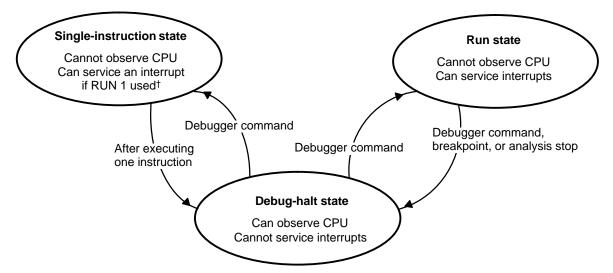

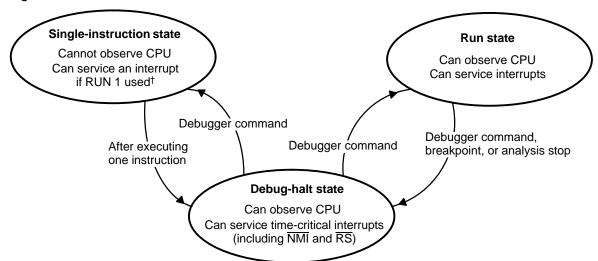

| 7–2  | Stop Mode Execution States                                               | 7-8  |

| 7–3  | Real-time Mode Execution States                                          | 7-10 |

| 7–4  | Stop Mode Versus Real-Time Mode                                          | 7-12 |

| 7–5  | Process for Handling a DT-DMA Request                                    | 7-17 |

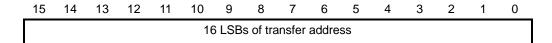

| 7–6  | ADDRL (at Data-Space Address 00 083816)                                  | 7-24 |

| 7–7  | ADDRH (at Data-Space Address 00 083916)                                  | 7-24 |

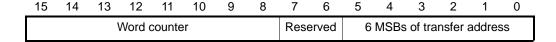

| 7–8  | REFL (at Data-Space Address 00 084A16)                                   | 7-24 |

| 7–9  | REFH (at Data-Space Address 00 084B16)                                   | 7-24 |

| 7–10 | Valid Combinations of Analysis Resources                                 | 7-30 |

| A-1  | Status register ST0                                                      | A-4  |

| A-2  | Status register ST1, Bits15–8                                            | A-5  |

| A-3  | Status Register ST1, Bits 7–0                                            | A-6  |

| A-4  | Interrupt flag register (IFR)                                            | A-7  |

| A-5 | Interrupt enable register (IER)                         | A-8  |

|-----|---------------------------------------------------------|------|

| A-6 | Debug interrupt enable register (DBGIER)                | A-9  |

| B-1 | Register Changes From C2xLP to C28x                     | B-3  |

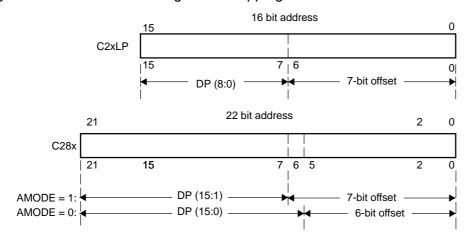

| B-2 | Direct Addressing Mode Mapping                          | B-6  |

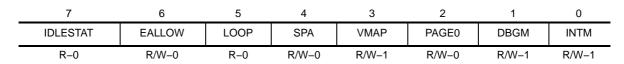

| B-3 | Status Register Comparison Between C2xLP and C28x       | B-7  |

| B-4 | Memory Map Comparison (See Note A)                      | B-13 |

| C-1 | Flow Chart of Recommended Migration Steps               |      |

| E-1 | C28x Registers                                          | E-2  |

| E-2 | Full Context Save/Restore                               | E-5  |

| E-3 | Code for a Full Context Save/Restore for C28x vs C27x   | E-6  |

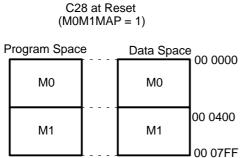

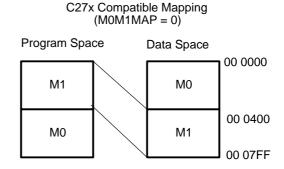

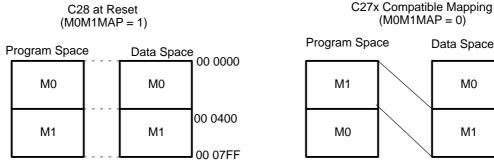

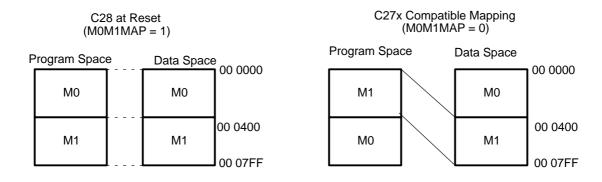

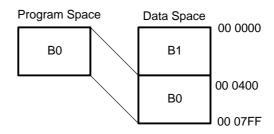

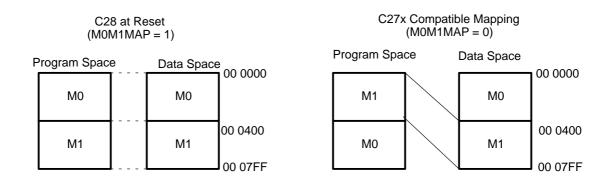

| E-4 | Mapping of Memory Blocks B0 and B1 on C27x              | E-7  |

| E-5 | C27x Compatible Mapping of Blocks M0 and M1             | E-7  |

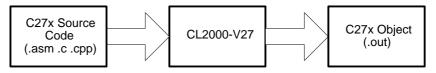

| E-6 | Building a C27x Object File From C27x Source            |      |

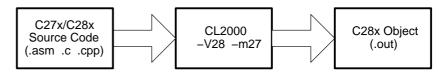

| E-7 | Building a C28x Object File From Mixed C27x/C28x Source | E-9  |

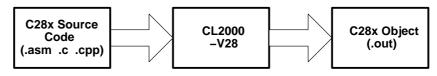

| F_8 | Compiling C28y Source                                   | F-16 |

# **Tables**

| 1–1  | Compatibility Modes                                                                            | 1-2  |

|------|------------------------------------------------------------------------------------------------|------|

| 1–2  | Summary of Bus Use During Data-Space and Program-Space Accesses                                |      |

| 1–3  | Special Bus Operations                                                                         |      |

| 2–1  | CPU Register Summary                                                                           | 2-4  |

| 2-2  | Available Operations for Shifting Values in the Accumulator                                    | 2-8  |

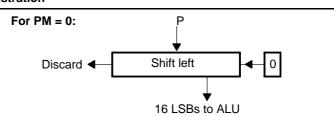

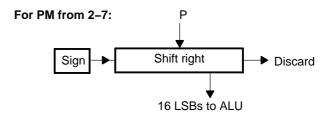

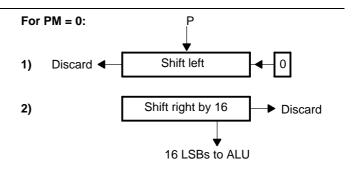

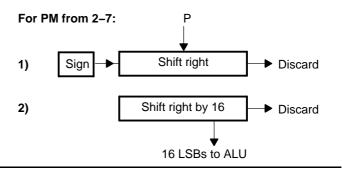

| 2-3  | Product Shift Modes                                                                            | 2-10 |

| 2-4  | Instructions That Affect OVC/OVCU                                                              | 2-17 |

| 2-5  | Instructions Affected by the PM Bits                                                           | 2-20 |

| 2–6  | Instructions Affected by V flag                                                                | 2-21 |

| 2–7  | Negative Flag Under Overflow Conditions                                                        | 2-24 |

| 2–8  | Bits Affected by the C Bit                                                                     | 2-25 |

| 2-9  | Instructions That Affect the TC Bit                                                            | 2-31 |

| 2-10 | Instructions Affected by SXM                                                                   | 2-33 |

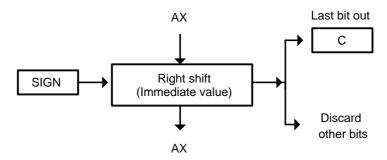

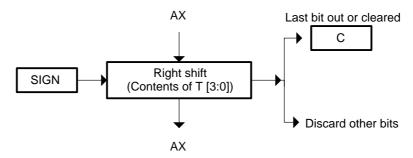

| 2–11 | Shift Operations                                                                               | 2-45 |

| 3–1  | Interrupt Vectors and Priorities                                                               | 3-4  |

| 3–2  | Requirements for Enabling a Maskable Interrupt                                                 | 3-7  |

| 3–3  | Register Pairs Saved and SP Positions for Context Saves                                        | 3-14 |

| 3-4  | Register Pairs Saved and SP Positions for Context Saves                                        | 3-20 |

| 3–5  | Registers After Reset                                                                          | 3-23 |

| 5–1  | Addressing Modes for "loc16" or "loc32"                                                        | 5-4  |

| 6–1  | Instruction Set Summary (Organized by Function)                                                | 6-2  |

| 6–2  | Register Operations                                                                            | 6-4  |

| 7–1  | 14-Pin Header Signal Descriptions                                                              | 7-4  |

| 7–2  | Selecting Device Operating Modes By Using TRST, EMU0, and EMU1                                 | 7-5  |

| 7–3  | Interrupt Handling Information By Mode and State                                               | 7-13 |

| 7–4  | Start Address and DMA Registers                                                                | 7-25 |

| 7–5  | End-Address Registers                                                                          | 7-26 |

| 7–6  | Analysis Resources                                                                             | 7-30 |

| A-1  | Reset Values of the Status and Control Registers                                               |      |

| B-1  | General Features                                                                               |      |

| B-2  | C2xLP Product Mode Shifter                                                                     | B-8  |

| B-3  | C28x Product Mode Shifter                                                                      | B-8  |

| B-4  | Reset Conditions of Internal Registers                                                         | B-10 |

| B-5  | Status Register Bits                                                                           | B-11 |

| B-6  | B0 Memory Map                                                                                  | B-14 |

| C-1  | Code to Save Contents Of IMR (IER) And Disabling Lower Priority Interrupts At Beginning Of ISR | C-7  |

| C-2  | Code to Disable an Interrupt                             | C-7  |

|------|----------------------------------------------------------|------|

| C-3  | Code to Enable an Interrupt                              | C-8  |

| C-4  | Code to Clear the IFR Register                           | C-8  |

| C-5  | Full Context Save/Restore Comparison                     | C-9  |

| C-6  | C2xLP and C28x Differences in Interrupts                 |      |

| C-7  | C2xLP and C28x Differences in Status Registers           |      |

| C-8  | C2xLp and C28x Differences in Memory Maps                |      |

| C-9  | C2xLP and C28x Differences in Instructions and Registers | C-13 |

| C-10 | Code Generation Tools and Syntax Differences             | C-15 |

| D-1  | C28x and C2xLP Flags                                     | D-2  |

| D-2  | C2xLP Instructions and C28x Equivalent Instructions      |      |

| D-3  | Repeatable Instructions for the C2xLP and C28x           |      |

| E-1  | ST0 Register Bits                                        | E-3  |

| E-2  | ST1 Register Bits                                        |      |

| E-3  | Instruction Syntax Change                                |      |

# **Examples**

| 3–1 | Typical ISR                                                       | 3-16 |

|-----|-------------------------------------------------------------------|------|

| 4–1 | Relationship Between Pipeline and Address Counters FC, IC, and PC | 4-6  |

| 4–2 | Diagramming Pipeline Activity                                     | 4-8  |

| 4–3 | Simplified Diagram of Pipeline Activity                           | 4-9  |

| 4–4 | Conflict Between a Read From and a Write to Same Memory Location  | 4-13 |

| 4–5 | Register Conflict                                                 | 4-14 |

| 7–1 | Initialization Code for Data Logging With Word Counter            | 7-28 |

| 7–2 | Initialization Code for Data Logging With End Address             | 7-29 |

## **Chapter 1**

## **Architectural Overview**

The TMS320C28 $x^{\text{\tiny M}}$  is one of several fixed-point CPUs in the TMS320 family. The C28 $x^{\text{\tiny M}}$  is source-code and object-code compatible with the C27 $x^{\text{\tiny M}}$ . In addition, much of the code written for the C2xLP CPU can be reassembled to run on a C28x device.

The C2xLP CPU is used in all TMS320F24xx and TMS320C20x devices and their derivatives. This document refers to C2xLP as a generic name for the CPU used in these devices.

This chapter provides an overview of the architectural structure and components of the C28x CPU.

| •   |                            |                                                                                                                          |

|-----|----------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 1.1 | Introduction to the CPU1-2 | )                                                                                                                        |

| 1.2 | Components of the CPU 1-4  | Ļ                                                                                                                        |

| 1.3 | Memory Map 1-7             | ,                                                                                                                        |

| 1.4 | Memory Interface 1-9       | )                                                                                                                        |

|     | 1.1<br>1.2<br>1.3          | Topic Page  1.1 Introduction to the CPU 1-2  1.2 Components of the CPU 1-4  1.3 Memory Map 1-7  1.4 Memory Interface 1-9 |

### 1.1 Introduction to the CPU

The CPU is a low-cost 32-bit fixed-point processor. This device draws from the best features of digital signal processing; reduced instruction set computing (RISC); and microcontroller architectures, firmware, and tool sets. The CPU features include a modified Harvard architecture and circular addressing. The RISC features are single-cycle instruction execution, register-to-register operations, and modified Harvard architecture (usable in Von Neumann mode). The microcontroller features include ease of use through an intuitive instruction set, byte packing and unpacking, and bit manipulation.

The modified Harvard architecture of the CPU enables instruction and data fetches to be performed in parallel. The CPU can read instructions and data while it writes data simultaneously to maintain the single-cycle instruction operation across the pipeline. The CPU does this over six separate address/data buses.

### 1.1.1 Compatibility With Other TMS320 CPUs

The C28x CPU features compatibility modes that minimize the migration effort from the C27x and C2xLP CPUs. The operating mode of the device is determined by a combination of the OBJMODE and AMODE bits in status register 1 (ST1) as shown in Table 1–1. The OBJMODE bit allows you to select between code compiled for a C28x (OBJMODE == 1) and code compiled for a C27x (OBJMODE == 0). The AMODE bit allows you to select between C28x/C27x instruction addressing modes (AMODE == 0) and C2xLP compatible instruction addressing modes (AMODE == 1).

Table 1-1. Compatibility Modes

|                              | OBJMODE | AMODE |

|------------------------------|---------|-------|

| C28x Mode                    | 1       | 0     |

| C2xLP Source-compatible Mode | 1       | 1     |

| C27x Object-compatible Mode† | 0       | 0     |

<sup>&</sup>lt;sup>†</sup> The C28x is in C27x-compatible mode at reset.

□ C28x Mode: In C28x mode, you can take advantage of all the C28x native features, addressing modes, and instructions. To operate in C28x mode from reset, your code must first set the OBJMODE bit by using the "C28OBJ" (or "SETC OBJMODE") instruction. This book assumes you are operating in C28x mode unless stated otherwise.

- □ C2xLP Source-Compatible Mode: C2xLP source-compatible mode allows you to run C2xLP source code which has been reassembled using the C28x code-generation tools. For more information on operating in this mode and migration from a C2xLP CPU, see Appendices C, D, and E.

- □ C27x Object-Compatible Mode: At reset, the C28x CPU operates in C27x object-compatible mode. In this mode, the C28x is 100% object-code and cycle-count compatible with the C27x CPU. For detailed information on operating in C27x object-compatible mode and migrating from the C27x, see Appendix F.

### 1.1.2 Switching to C28x Mode From Reset

At reset, the C28x CPU is in C27x Object-Compatible Mode (OBJMODE == 0, AMODE == 0) and is 100% compatible with the C27x CPU. To take advantage of the enhanced C28x instruction set, you must instead operate the device in C28x mode. To do this, after a reset your code must first set the OBJMODE bit in ST1 by using the "C28OBJ" (or "SETC OBJMODE") instruction.

### 1.2 Components of the CPU

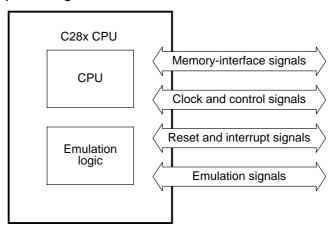

As shown in Figure 1–1, the CPU contains:

- □ A CPU for generating data- and program-memory addresses; decoding and executing instructions; performing arithmetic, logical, and shift operations; and controlling data transfers among CPU registers, data memory, and program memory

- ☐ Emulation logic for monitoring and controlling various parts and functionalities of the DSP and for testing device operation

- ☐ Signals for interfacing with memory and peripherals, clocking and controlling the CPU and the emulation logic, showing the status of the CPU and the emulation logic, and using interrupts

The CPU does not contain memory, a clock generator, or peripheral devices. For information about interfacing to these items, see the *C28x Peripheral User's Guide* (literature number SPRU566) and the data sheet that corresponds to your DSP.

Figure 1-1. High-Level Conceptual Diagram of the CPU

### 1.2.1 Central Processing Unit (CPU)

The CPU is discussed in more detail in Chapter 2, but following is a list of its major features:

- Protected pipeline. The CPU implements an 8-phase pipeline that prevents a write to and a read from the same location from occurring out of order.

- Independent register space. The CPU contains registers that are not mapped to data space. These registers function as system-control

registers, math registers, and data pointers. The system-control registers are accessed by special instructions. The other registers are accessed by special instructions or by a special addressing mode (register addressing mode). Arithmetic logic unit (ALU). The 32-bit ALU performs 2s-complement arithmetic and Boolean logic operations. Address register arithmetic unit (ARAU). The ARAU generates datamemory addresses and increments or decrements pointers in parallel with ALU operations. Barrel shifter. This shifter performs all left and right shifts of data. It can shift data to the left by up to 16 bits and to the right by up to 16 bits. ☐ Multiplier. The multiplier performs 32-bit × 32-bit 2s-complement multiplication with a 64-bit result. The multiplication can be performed with two signed numbers, two unsigned numbers, or one signed number and one unsigned number. 1.2.2 Emulation Logic The emulation logic includes the following features. For more details about these features, see Chapter 7, Emulation Features. ☐ Debug-and-test direct memory access (DT-DMA). A debug host can gain direct access to the content of registers and memory by taking control of the memory interface during unused cycles of the instruction pipeline. ☐ Data logging. The emulation logic enables application-initiated transfers of memory contents between the C28x and a debug host. ☐ A counter for performance benchmarking ☐ Multiple debug events. Any of the following *debug events* can cause a break in program execution: ■ A breakpoint initiated by the ESTOP0 or ESTOP1 instruction ■ An access to a specified program-space or data-space location A request from the debug host or other hardware When a debug event causes the C28x to enter the debug-halt state, the event is called a break event. Real-time mode of operation. When the C28x is in this mode and a break

event occurs, the main body of program code comes to a halt, but time-crit-

ical interrupts can still be serviced.

### 1.2.3 Signals

The CPU has four main types of signals:

Memory-interface signals. These signals transfer data among the CPU, memory, and peripherals; indicate program-memory accesses and data-memory accesses; and differentiate between accesses of different sizes (16-bit or 32-bit).

Clock and control signals. These provide clocking for the CPU and the emulation logic, and they are used to control and monitor the CPU.

Reset and interrupt signals. These are used for generating a hardware reset and interrupts, and for monitoring the status of interrupts.

Emulation signals. These signals are used for testing and debugging.

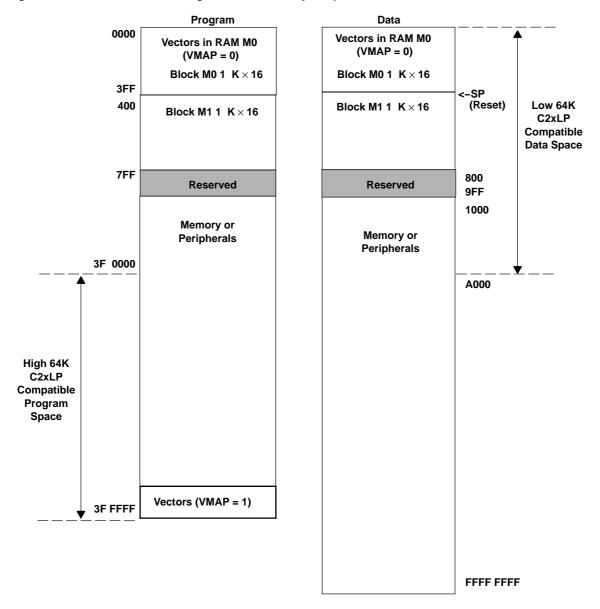

### 1.3 Memory Map

The C28x uses 32-bit data addresses and 22-bit program addresses. This allows for a total address reach of 4G words (1 word = 16 bits) in data space and 4M words in program space. Memory blocks on all C28x designs are uniformly mapped to both program and data space. Figure 1–2 shows a high-level view of how addresses are allocated in program space and data space.

| The | e memory map in Figure 1–2 has been divided into the following segments |

|-----|-------------------------------------------------------------------------|

|     | On-chip program/data                                                    |

|     | Reserved                                                                |

|     | CPU interrupt vectors                                                   |

|     |                                                                         |

For specific details about each of the map segments, see the data sheet for your device. See Appendix C for more information on the C2xLP compatible memory space.

### 1.3.1 CPU Interrupt Vectors

Sixty-four addresses in program space are set aside for a table of 32 CPU interrupt vectors. The CPU vectors can be mapped to the top or bottom of program space by way of the VMAP bit. For more information about the CPU vectors, see Section 3.2, *Interrupt Vectors and Priorities* on page 3-4.

For devices with a peripheral interrupt expansion (PIE) block, the interrupt vectors will reside in the PIE vector table and this memory can be used as program memory.

Figure 1-2. TMS320C28x High-Level Memory Map

See the data sheet for your specific device for details of the exact memory map.

### 1.4 Memory Interface

The C28x memory map is accessible outside the CPU by the memory interface, which connects the CPU logic to memories, peripherals, or other interfaces. The memory interface includes separate buses for program space and data space. This means an instruction can be fetched from program memory while data memory is being accessed.

The interface also includes signals that indicate the type of read or write being requested by the CPU. These signals can select a specified memory block or peripheral for a given bus transaction. In addition to 16-bit and 32-bit accesses, the C28x supports special byte-access instructions which can access the least significant byte (LSByte) or most significant byte (MSByte) of an addressed word. Strobe signals indicate when such an access is occurring on a data bus.

#### 1.4.1 Address and Data Buses

The memory interface has three address buses:

- **PAB** Program address bus. The PAB carries addresses for reads and writes from program space. PAB is a 22-bit bus.

- **DRAB** Data-read address bus. The 32-bit DRAB carries addresses for reads from data space.

- **DWAB** Data-write address bus. The 32-bit DWAB carries addresses for writes to data space.

The memory interface also has three data buses:

- **PRDB** Program-read data bus. The PRDB carries instructions or data during reads from program space. PRDB is a 32-bit bus.

- **DRDB** Data-read data bus. The DRDB carries data during reads from data space. PRDB is a 32-bit bus.

- **DWDB** Data-/Program-write data bus. The 32-bit DWDB carries data during writes to data space or program space.

Table 1–2 summarizes how these buses are used during accesses.

Table 1–2. Summary of Bus Use During Data-Space and Program-Space Accesses

| Access Type             | Address Bus | Data Bus |

|-------------------------|-------------|----------|

| Read from program space | PAB         | PRDB     |

| Read from data space    | DRAB        | DRDB     |

| Write to program space  | PAB         | DWDB     |

| Write to data space     | DWAB        | DWDB     |

A program-space read and a program-space write cannot happen simultaneously because both use the PAB. Similarly, a program-space write and a data-space write cannot happen simultaneously because both use the DWDB. Transactions that use different buses can happen simultaneously. For example, the CPU can read from program space (using PAB and PRDB), read from data space (using DRAB and DRDB), and write to data space (using DWAB and DWDB) at the same time.

### 1.4.2 Special Bus Operations

Typically, PAB and PRDB are used only for reading instructions from program space, and DWDB is used only for writing data to data space. However, the instructions in Table 1–3 are exceptions to this behavior. For more details about using these instructions, see Chapter 6, *Assembly Language Instructions*.

Table 1-3. Special Bus Operations

| Instruction                     | Special Bus Operation                                                                                                                                                                                                                         |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PREAD                           | This instruction reads a data value rather than an instruction from program space. It then transfers that value to data space or a register.                                                                                                  |

|                                 | For the read from program space, the CPU places the source address on the program address bus (PAB), sets the appropriate program-space select signals, and reads the data value from the program-read data bus (PRDB).                       |

| PWRITE                          | This instruction writes a data value to program space. The value is read from from data space or a register.                                                                                                                                  |

|                                 | For the write to program space, the CPU places the destination address on the program address bus (PAB), sets the appropriate program-space select signals, and writes the data value to the data-/program-write data bus (DWDB).             |

| MAC<br>DMAC                     | As part of their operation, these instructions multiply two data values, one of which is read from program space.                                                                                                                             |

| QMACL<br>IMACL<br>XMAC<br>XMACD | For the read from program space, the CPU places the program-space source address on the program address bus (PAB), sets the appropriate program-space select signals, and reads the program data value from the program read data bus (PRDB). |

### 1.4.3 Alignment of 32-Bit Accesses to Even Addresses

The C28x CPU expects memory wrappers or peripheral-interface logic to align any 32-bit read or write to an even address. If the address-generation logic generates an odd address, the CPU must begin reading or writing at the previous even address. This alignment does not affect the address values generated by the address-generation logic.

Most instruction fetches from program space are performed as 32-bit read operations and are aligned accordingly. However, alignment of instruction fetches are effectively invisible to a programmer. When instructions are stored to program space, they do not have to be aligned to even addresses. Instruction boundaries are decoded within the CPU.

You need to be concerned with alignment when using instructions that perform 32-bit reads from or writes to data space.

# **Central Processing Unit**

The central processing unit (CPU) is responsible for controlling the flow of a program and the processing of instructions. It performs arithmetic, Boolean-logic, multiply, and shift operations. When performing signed math, the CPU uses 2s-complement notation. This chapter describes the architecture, registers, and primary functions of the CPU.

| Topic | <b>c</b> I          | Page  |

|-------|---------------------|-------|

| 2.1   | CPU Architecture    | . 2-2 |

| 2.2   | CPU Registers       | . 2-4 |

| 2.3   | Status Register ST0 | 2-16  |

| 2.4   | Status Register ST1 | 2-34  |

| 2.5   | Program Flow        | 2-39  |

| 2.6   | Multiply Operations | 2-41  |

| 2.7   | Shift Operations    | 2-44  |

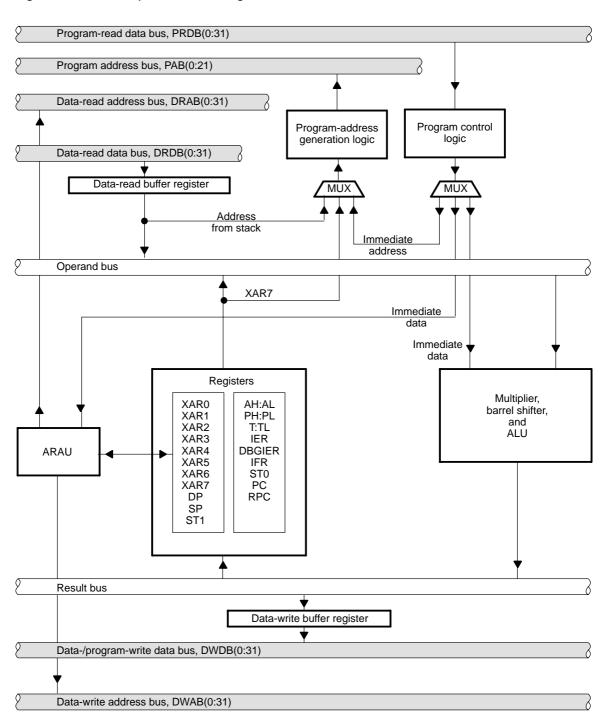

### 2.1 CPU Architecture

All C28x devices contain a central processing unit (CPU), emulation logic, and signals for interfacing with memory and peripherals. Included with these signals are three address buses and three data buses. Figure 2–1 shows the major blocks and data paths of the C28x CPU. It does not reflect the actual silicon implementation. The shaded buses are memory-interface buses that are external to the CPU. The operand bus supplies the values for multiplier, shifter, and ALU operations, and the result bus carries the results to registers and memory. The main blocks of the CPU are:

| and | nal to the CPU. The operand bus supplies the values for multiplier, shifter, d ALU operations, and the result bus carries the results to registers and mory. The main blocks of the CPU are:                                                                                                                                                                                                                                       |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | <b>Program and data control logic.</b> This logic stores a queue of instructions that have been fetched from program memory.                                                                                                                                                                                                                                                                                                       |

|     | Real-Time emulation and visibility                                                                                                                                                                                                                                                                                                                                                                                                 |

|     | Address register arithmetic unit (ARAU). The ARAU generates addresses for values that must be fetched from data memory. For a data read, it places the address on the data-read address bus (DRAB); for a data write, it loads the data-write address bus (DWAB). The ARAU also increments or decrements the stack pointer (SP) and the auxiliary registers (XAR0, XAR1, XAR2, XAR3, XAR4, XAR5, XAR6, and XAR7).                  |

|     | <b>Atomic arithmetic logic unit (ALU).</b> The 32-bit ALU performs 2s-complement arithmetic and Boolean logic operations. Before doing its calculations, the ALU accepts data from registers, from data memory, or from the program control logic. The ALU saves results to a register or to data memory.                                                                                                                          |

|     | Prefetch queue and instruction decode                                                                                                                                                                                                                                                                                                                                                                                              |

|     | Address generators for program and data                                                                                                                                                                                                                                                                                                                                                                                            |

|     | <b>Fixed-point MPY/ALU</b> . The multiplier performs 32-bit $\times$ 32-bit 2s-complement multiplication with a 64-bit result. In conjunction with the multiplier, the '28xx uses the 32-bit multiplicand register (XT), the 32-bit product register (P), and the 32-bit accumulator (ACC). The XT register supplies one of the values to be multiplied. The result of the multiplication can be sent to the P register or to ACC. |

|     | Interrupt processing                                                                                                                                                                                                                                                                                                                                                                                                               |

Figure 2-1. Conceptual Block Diagram of the CPU

### 2.2 CPU Registers

Table 2–1 lists the main CPU registers and their values after reset. Sections 2.2.1 through 2.2.10 describe the registers in more detail. Figure 2–2 shows the registers.

Table 2-1. CPU Register Summary

| Register | Size    | Description          | Value After Reset |

|----------|---------|----------------------|-------------------|

| ACC      | 32 bits | Accumulator          | 0x00000000        |

| AH       | 16 bits | High half of ACC     | 0x0000            |

| AL       | 16 bits | Low half of ACC      | 0x0000            |

| XAR0     | 16 bits | Auxiliary register 0 | 0x00000000        |

| XAR1     | 32 bits | Auxiliary register 1 | 0x00000000        |

| XAR2     | 32 bits | Auxiliary register 2 | 0x00000000        |

| XAR3     | 32 bits | Auxiliary register 3 | 0x00000000        |

| XAR4     | 32 bits | Auxiliary register 4 | 0x00000000        |

| XAR5     | 32 bits | Auxiliary register 5 | 0x00000000        |

| XAR6     | 32 bits | Auxiliary register 6 | 0x0000000         |

| XAR7     | 32 bits | Auxiliary register 7 | 0x0000000         |

| AR0      | 16 bits | Low half of XAR0     | 0x0000            |

| AR1      | 16 bits | Low half of XAR1     | 0x0000            |

| AR2      | 16 bits | Low half of XAR2     | 0x0000            |

| AR3      | 16 bits | Low half of XAR3     | 0x0000            |

| AR4      | 16 bits | Low half of XAR4     | 0x0000            |

| AR5      | 16 bits | Low half of XAR5     | 0x0000            |

| AR6      | 16 bits | Low half of XAR6     | 0x0000            |

| AR7      | 16 bits | Low half of XAR7     | 0x0000            |

Table 2–1. CPU Register Summary (Continued)

| Register | Size    | Description                     | Value After Reset                                 |

|----------|---------|---------------------------------|---------------------------------------------------|

| DP       | 16 bits | Data-page pointer               | 0x0000                                            |

| IFR      | 16 bits | Interrupt flag register         | 0x0000                                            |

| IER      | 16 bits | Interrupt enable register       | 0x0000 (INT1 to INT14, DLOGINT, RTOSINT disabled) |

| DBGIER   | 16 bits | Debug interrupt enable register | 0x0000 (INT1 to INT14, DLOGINT, RTOSINT disabled) |

| Р        | 32 bits | Product register                | 0x00000000                                        |

| PH       | 16 bits | High half of P                  | 0x0000                                            |

| PL       | 16 bits | Low half of P                   | 0x0000                                            |

| PC       | 22 bits | Program counter                 | 0x3F FFC0                                         |

| RPC      | 22 bits | Return program counter          | 0x00000000                                        |

| SP       | 16 bits | Stack pointer                   | 0x0400                                            |

| ST0      | 16 bits | Status register 0               | 0x0000                                            |

| ST1      | 16 bits | Status register 1               | 0x080B†                                           |

|          |         |                                 |                                                   |

| XT       | 32 bits | Multiplicand register           | 0x00000000                                        |

| Т        | 16 bits | High half of XT                 | 0x0000                                            |

| TL       | 16 bits | Low half of XT                  | 0x0000                                            |

$<sup>^\</sup>dagger$  Reset value shown is for devices without the VMAP signal and MOM1MAP signal pinned out. On these devices both of these signals are tied high internal to the device.

Figure 2-2. C28x Registers

| T[16]  | TL[16] | XT[32]  |

|--------|--------|---------|

| PH[16] | PL[16] | P[32]   |

| AH[16] | AL[16] | ACC[32] |

|          |       | SP[16]  |                    |          |

|----------|-------|---------|--------------------|----------|

|          | DPI   | [16]    | 6/7-bit<br>offset† |          |

| AR0H[16] |       | AR0[16] |                    | XAR0[32] |

| AR1H[16] |       | AR1[16] |                    | XAR1[32] |

| AR2H[16] |       | AR2[16] |                    | XAR2[32] |

| AR3H[16] |       | AR3[16] |                    | XAR3[32] |

| AR4      | H[16] | AR4[    | 16]                | XAR4[32] |

| AR5H[16] |       | AR5[16] |                    | XAR5[32] |

| AR6H[16] |       | AR6[16] |                    | XAR6[32] |

| AR7H[16] |       | AR7[16] |                    | XAR7[32] |

|          |       | PC[22]  |                    |          |

| RPC[22]  |       |         |                    |          |

|          |       |         |                    | _        |

| ST0[16] |

|---------|

| ST1[16] |

| IER[16]    |

|------------|

| DBGIER[16] |

| IFR[16]    |

<sup>&</sup>lt;sup>†</sup> A 6-bit offset is used when operating in C28x mode or C27x object-compatible mode. A 7-bit offset is used when operating in C2xLP source-compatible mode. The least significant bit of the DP is ignored when operating in this mode.

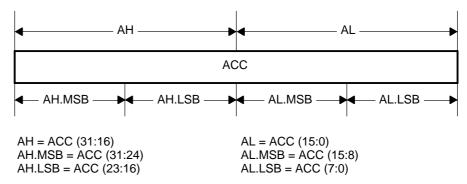

### 2.2.1 Accumulator (ACC, AH, AL)

The accumulator (ACC) is the main working register for the device. It is the destination for all ALU operations except those which operate directly on memory or registers. ACC supports single-cycle move, add, subtract, and

compare operations from 32-bit-wide data memory. It can also accept the 32-bit result of a multiplication operation.

The halves and quarters of the ACC can also be accessed (see Figure 2–3). ACC can be treated as two independent 16-bit registers: AH (high 16 bits) and AL (low 16 bits). The bytes within AH and AL can also be accessed independently. Special byte-move instructions load and store the most significant byte or least significant byte of AH or AL. This enables efficient byte packing and unpacking.

Figure 2-3. Individually Accessible Portions of the Accumulator

The accumulator has the following associated status bits. For the details on these bits, see section 2.3, *Status Register ST0*.

- ☐ Overflow mode bit (OVM)

- ☐ Sign-extension mode bit (SXM)

- ☐ Test/control flag bit (TC)

- ☐ Carry bit (C)

- ☐ Zero flag bit (Z)

- ☐ Negative flag bit (N)

- □ Latched overflow flag bit (V)

- ☐ Overflow counter bits (OVC)

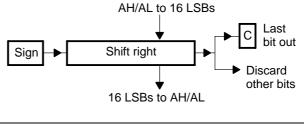

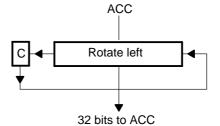

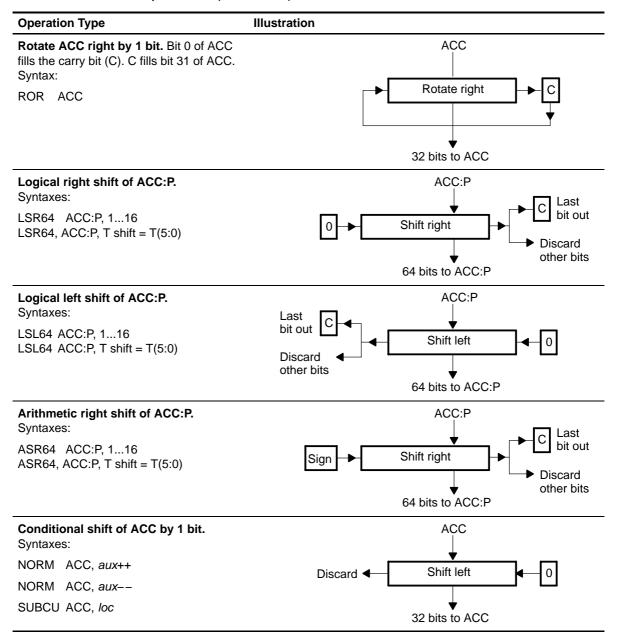

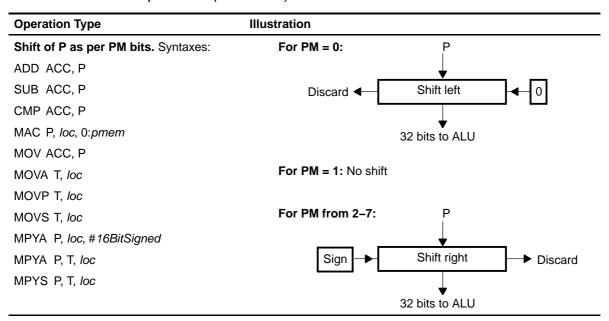

Table 2–2 shows the ways to shift the content of AH, AL, or ACC.

Table 2–2. Available Operations for Shifting Values in the Accumulator

| Register | Shift Direction | Shift Type | Instruction                 |

|----------|-----------------|------------|-----------------------------|

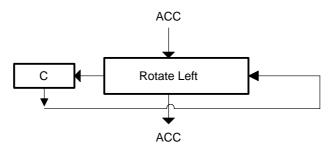

| ACC      | Left            | Logical    | LSL or LSLL                 |

|          |                 | Rotation   | ROL                         |

|          | Right           | Arithmetic | SFR with SXM = 1<br>or ASRL |

|          |                 | Logical    | SFR with SXM = 0 or LSRL    |

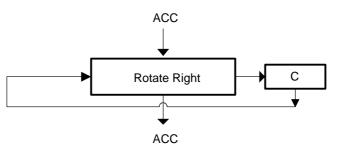

|          |                 | Rotation   | ROR                         |

| AH or AL | Left            | Logical    | LSL                         |

|          | Right           | Arithmetic | ASR                         |

|          |                 | Logical    | LSR                         |

## 2.2.2 Multiplicand Register (XT)

The multiplicand register (XT register) is used primarily to store a 32-bit signed integer value prior to a 32-bit multiply operation.