# TMS320C28x Floating Point Unit and Instruction Set

## **Reference Guide**

Literature Number: SPRUEO2A June 2007–Revised August 2008

## Contents

| Prefa | ice                                                      |  |  |  |  |  |

|-------|----------------------------------------------------------|--|--|--|--|--|

| 1     | Introduction7                                            |  |  |  |  |  |

| 1.1   | Introduction to the Central Processing Unit (CPU)        |  |  |  |  |  |

| 1.2   | Compatibility with the C28x Fixed-Point CPU              |  |  |  |  |  |

|       | 1.2.1 Floating-Point Code Development                    |  |  |  |  |  |

| 1.3   | Components of the C28x plus Floating-Point CPU           |  |  |  |  |  |

|       | 1.3.1 Emulation Logic 10                                 |  |  |  |  |  |

|       | 1.3.2 Memory Map 10                                      |  |  |  |  |  |

|       | 1.3.3 On-Chip Program and Data 10                        |  |  |  |  |  |

|       | 1.3.4 CPU Interrupt Vectors 10                           |  |  |  |  |  |

| 1.4   | Memory Interface 10                                      |  |  |  |  |  |

|       | 1.4.1 Address and Data Buses 11                          |  |  |  |  |  |

|       | 1.4.2 Alignment of 32-Bit Accesses to Even Addresses 11  |  |  |  |  |  |

| 2     | CPU Register Set 13                                      |  |  |  |  |  |

| 2.1   | CPU Registers 14                                         |  |  |  |  |  |

|       | 2.1.1 Floating-Point Status Register (STF) 16            |  |  |  |  |  |

|       | 2.1.2 Repeat Block Register (RB) 18                      |  |  |  |  |  |

| 3     | Pipeline                                                 |  |  |  |  |  |

| 3.1   | Pipeline Overview                                        |  |  |  |  |  |

| 3.2   | General Guidelines for Floating-Point Pipeline Alignment |  |  |  |  |  |

| 3.3   | Moves from FPU Registers to C28x Registers               |  |  |  |  |  |

| 3.4   | Moves from C28x Registers to FPU Registers               |  |  |  |  |  |

| 3.5   | Parallel Instructions                                    |  |  |  |  |  |

| 3.6   | Invalid Delay Instructions                               |  |  |  |  |  |

| 3.7   | Optimizing the Pipeline 27                               |  |  |  |  |  |

| 4     | Instruction Set                                          |  |  |  |  |  |

| 4.1   | Instruction Descriptions                                 |  |  |  |  |  |

| 4.2   | Instructions 32                                          |  |  |  |  |  |

| Α     | Revision History 137                                     |  |  |  |  |  |

| A.1   | Changes 137                                              |  |  |  |  |  |

#### List of Figures

| 1-1 | FPU Functional Block Diagram              | 8  |

|-----|-------------------------------------------|----|

|     | C28x With Floating-Point Registers        |    |

|     | Floating-point Unit Status Register (STF) |    |

| 2-3 | Repeat Block Register (RB)                | 18 |

| 3-1 | FPU Pipeline                              | 22 |

#### List of Tables

| 2-1 | 28x Plus Floating-Point CPU Register Summary                 | 15  |

|-----|--------------------------------------------------------------|-----|

|     | Floating-point Unit Status (STF) Register Field Descriptions |     |

| 2-3 | Repeat Block (RB) Register Field Descriptions                | 18  |

| 4-1 | Operand Nomenclature                                         | 30  |

| 4-2 | Summary of Instructions                                      | 32  |

| A-1 | Technical Changes Made in This Revision                      | 137 |

Preface SPRUE02A–June 2007–Revised August 2008

This document describes the CPU architecture, pipeline, instruction set, and interrupts of the C28x floating-point DSP.

#### About This Manual

The TMS320C2000<sup>™</sup> digital signal processor (DSP) platform is part of the TMS320<sup>™</sup> DSP family.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h or with a leading 0x. For example, the following number is 40 hexadecimal (decimal 64): 40h or 0x40.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation**

The following books describe the TMS320x28x and related support tools that are available on the TI website:

#### Data Manual and Errata—

SPRS439— <u>TMS320F28335</u>, <u>TMS320F28334</u>, <u>TMS320F28332</u>, <u>TMS320F28235</u>, <u>TMS320F28235</u>, <u>TMS320F28232</u>, <u>TMS320F28232</u> <u>Digital Signal Controllers (DSCs) Data Manual</u> contains the pinout, signal descriptions, as well as electrical and timing specifications for the F2833x/2823x devices.

SPRZ272— TMS320F28335, F28334, F28332, TMS320F28235, F28234, F28232 Digital Signal Controllers (DSCs) Silicon Errata describes the advisories and usage notes for different versions of silicon.

#### CPU User's Guides—

- **SPRU430** <u>TMS320C28x DSP CPU and Instruction Set Reference Guide</u> describes the central processing unit (CPU) and the assembly language instructions of the TMS320C28x fixed-point digital signal processors (DSPs). It also describes emulation features available on these DSPs.

- **SPRUEO2** <u>TMS320C28x Floating Point Unit and Instruction Set Reference Guide</u> describes the floating-point unit and includes the instructions for the FPU.

#### Peripheral Guides—

- **SPRU566** <u>TMS320x28xx, 28xxx Peripheral Reference Guide</u> describes the peripheral reference guides of the 28x digital signal processors (DSPs).

- **SPRUFB0** <u>TMS320x2833x</u>, <u>2823x</u> <u>System Control and Interrupts Reference Guide</u> describes the various interrupts and system control features of the 2833x digital signal controllers (DSCs).</u>

- **SPRU812** <u>TMS320x2833x</u>, <u>2823x</u> <u>Analog-to-Digital Converter (ADC)</u> <u>Reference Guide</u> describes how to configure and use the on-chip ADC module, which is a 12-bit pipelined ADC.</u>

Related Documentation

www.ti.com

- **SPRU949** <u>TMS320x2833x, 2823x External Interface (XINTF) User's Guide</u> describes the XINTF, which is a nonmultiplexed asynchronous bus, as it is used on the 2833x devices.

- SPRU963— <u>TMS320x2833x</u>, <u>TMS320x2823x</u> Boot ROM User's Guide describes the purpose and features of the bootloader (factory-programmed boot-loading software) and provides examples of code. It also describes other contents of the device on-chip boot ROM and identifies where all of the information is located within that memory.

- SPRUFB7— <u>TMS320x2833x, 2823x Multichannel Buffered Serial Port (McBSP) User's Guide</u> describes the McBSP available on the F2833x devices. The McBSPs allow direct interface between a DSP and other devices in a system.

- **SPRUFB8** <u>TMS320x2833x, 2823x Direct Memory Access (DMA) Reference Guide</u> describes the DMA on the 2833x devices.

- SPRUG04— <u>TMS320x2833x</u>, 2823x Enhanced Pulse Width Modulator (ePWM) Module Reference Guide describes the main areas of the enhanced pulse width modulator that include digital motor control, switch mode power supply control, UPS (uninterruptible power supplies), and other forms of power conversion.

- **SPRUG02** <u>TMS320x2833x</u>, <u>2823x High-Resolution Pulse Width Modulator (HRPWM)</u> describes the operation of the high-resolution extension to the pulse width modulator (HRPWM).

- **SPRUFG4** <u>TMS320x2833x</u>, <u>2823x</u> <u>Enhanced Capture (eCAP) Module Reference Guide</u> describes the enhanced capture module. It includes the module description and registers.</u>

- **SPRUG05** <u>TMS320x2833x</u>, <u>2823x</u> Enhanced Quadrature Encoder Pulse (eQEP) Reference Guide describes the eQEP module, which is used for interfacing with a linear or rotary incremental encoder to get position, direction, and speed information from a rotating machine in high performance motion and position control systems. It includes the module description and registers.

- SPRUEU1— <u>TMS320x2833x</u>, <u>2823x</u> Enhanced Controller Area Network (eCAN) Reference Guide describes the eCAN that uses established protocol to communicate serially with other controllers in electrically noisy environments.

- SPRUFZ5— <u>TMS320F2833x, 2823x Serial Communication Interface (SCI) Reference Guide</u> describes the SCI, which is a two-wire asynchronous serial port, commonly known as a UART. The SCI modules support digital communications between the CPU and other asynchronous peripherals that use the standard non-return-to-zero (NRZ) format.

- SPRUEU3— TMS320x2833x, 2823x Serial Peripheral Interface (SPI) Reference Guide describes the SPI a high-speed synchronous serial input/output (I/O) port that allows a serial bit stream of programmed length (one to sixteen bits) to be shifted into and out of the device at a programmed bit-transfer rate.

- **SPRUG03** <u>TMS320x2833x, 2823x Inter-Integrated Circuit (I2C) Reference Guide</u> describes the features and operation of the inter-integrated circuit (I2C) module.

#### Tools Guides—

- SPRU513— <u>TMS320C28x Assembly Language Tools User's Guide</u> describes the assembly language tools (assembler and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for the TMS320C28x device.

- SPRU514— <u>TMS320C28x Optimizing C Compiler User's Guide</u> describes the TMS320C28x<sup>™</sup> C/C++ compiler. This compiler accepts ANSI standard C/C++ source code and produces TMS320 DSP assembly language source code for the TMS320C28x device.

- SPRU608— The TMS320C28x Instruction Set Simulator Technical Overview describes the simulator, available within the Code Composer Studio for TMS320C2000 IDE, that simulates the instruction set of the C28x<sup>™</sup> core.

- **SPRU625** <u>TMS320C28x DSP/BIOS Application Programming Interface (API) Reference Guide</u> describes development using DSP/BIOS.

## Introduction

The TMS320C2000<sup>™</sup> DSP family consists of fixed-point and floating-point digital signal controllers (DSCs). TMS320C2000<sup>™</sup> Digital Signal Controllers combine control peripheral integration and ease of use of a microcontroller (MCU) with the processing power and C efficiency of TI's leading DSP technology. This chapter provides an overview of the architectural structure and components of the C28x plus floating-point unit CPU.

| Торіс |                                                   | Page |

|-------|---------------------------------------------------|------|

| 1.1   | Introduction to the Central Processing Unit (CPU) | Q    |

| 1.2   | Compatibility with the C28x Fixed-Point CPU       |      |

| 1.3   | Components of the C28x plus Floating-Point CPU    |      |

| 1.4   | Memory Interface                                  |      |

|       | •                                                 |      |

7

#### 1.1 Introduction to the Central Processing Unit (CPU)

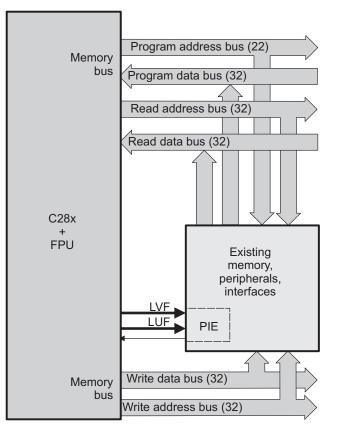

The C28x plus floating-point (C28x+FPU) processor extends the capabilities of the C28x fixed-point CPU by adding registers and instructions to support IEEE single-precision floating point operations. This device draws from the best features of digital signal processing; reduced instruction set computing (RISC); and microcontroller architectures, firmware, and tool sets. The DSC features include a modified Harvard architecture and circular addressing. The RISC features are single-cycle instruction execution, register-to-register operations, and modified Harvard architecture (usable in Von Neumann mode). The microcontroller features include ease of use through an intuitive instruction set, byte packing and unpacking, and bit manipulation. The modified Harvard architecture of the CPU enables instruction and data fetches to be performed in parallel. The CPU can read instructions and data while it writes data simultaneously to maintain the single-cycle instruction operation across the pipeline. The CPU does this over six separate address/data buses.

Throughout this document the following notations are used:

- C28x refers to the C28x fixed-point CPU.

- C28x plus Floating-Point and C28x+FPU both refer to the C28x CPU with enhancements to support IEEE single-precision floating-point operations.

#### 1.2 Compatibility with the C28x Fixed-Point CPU

No changes have been made to the C28x base set of instructions, pipeline, or memory bus architecture. Therefore, programs written for the C28x CPU are completely compatible with the C28x+FPU and all of the features of the C28x documented in *TMS320C28x DSP CPU and Instruction Set Reference Guide* (literature number <u>SPRU430</u>) apply to the C28x+FPU.

Figure 1-1 shows basic functions of the FPU.

#### Figure 1-1. FPU Functional Block Diagram

#### 1.2.1 Floating-Point Code Development

When developing C28x floating-point code use Code Composer Studio 3.3, or later, with at least service release 8. The C28x compiler V5.0, or later, is also required to generate C28x native floating-point opcodes. This compiler is available via Code Composer Studio update advisor as a seperate download. V5.0 can generate both fixed-point as well as floating-point code. To build floating-point code use the compiler switches:-v28 and - -float\_support = fpu32. In Code Composer Studio 3.3 the float\_support option is in the build options under compiler-> advanced: floating point support. Without the float\_support flag, or with float\_support = none, the compiler will generate fixed-point code.

When building for C28x floating-point make sure all associated libraries have also been built for floating-point. The standard run-time support (RTS) libaries built for floating-point included with the compiler have fpu32 in their name. For example rts2800\_fpu32.lib and rts2800\_fpu\_eh.lib have been built for the floating-point unit. The "eh" version has exception handling for C++ code. Using the fixed-point RTS libraries in a floating-point project will result in the linker issuing an error for incompatible object files.

To improve performance of native floating-point projects, consider using the *C28x FPU Fast RTS Library* (<u>SPRC664</u>). This library contains hand-coded optimized math routines such as division, square root, atan2, sin and cos. This library can be linked into your project before the standard runtime support library to give your application a performance boost. As an example, the standard RTS library uses a polynomial expansion to calculate the sin function. The Fast RTS library, however, uses a math look-up table in the boot ROM of the device. Using this look-up table method results in approximately a 20 cycle savings over the standard RTS calculation.

#### 1.3 Components of the C28x plus Floating-Point CPU

The C28x+FPU contains:

- A central processing unit for generating data and program-memory addresses; decoding and executing instructions; performing arithmetic, logical, and shift operations; and controlling data transfers among CPU registers, data memory, and program memory

- A floating-point unit for IEEE single-precision floating point operations.

- Emulation logic for monitoring and controlling various parts and functions of the device and for testing device operation. This logic is identical to that on the C28x fixed-point CPU.

- Signals for interfacing with memory and peripherals, clocking and controlling the CPU and the emulation logic, showing the status of the CPU and the emulation logic, and using interrupts. This logic is identical to the C28x fixed-point CPU.

Some features of the C28x+FPU central processing unit are:

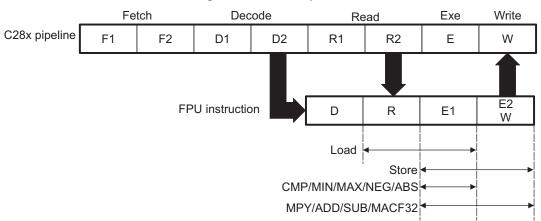

- Fixed-Point instructions are pipeline protected. This pipeline for fixed-point instructions is identical to that on the C28x fixed-point CPU. The CPU implements an 8-phase pipeline that prevents a write to and a read from the same location from occurring out of order. See Figure 3-1

- Some floating-point instructions require pipeline alignment. This alignment is done through software to allow the user to improve performance by taking advantage of required delay slots.

- Independent register space. These registers function as system-control registers, math registers, and data pointers. The system-control registers are accessed by special instructions.

- Arithmetic logic unit (ALU). The 32-bit ALU performs 2s-complement arithmetic and Boolean logic operations.

- Floating point unit (FPU). The 32-bit FPU performs IEEE single-precision floating-point operations.

- Address register arithmetic unit (ARAU). The ARAU generates data memory addresses and increments or decrements pointers in parallel with ALU operations.

- Barrel shifter. This shifter performs all left and right shifts of fixed-point data. It can shift data to the left by up to 16 bits and to the right by up to 16 bits.

- Fixed-Point Multiplier. The multiplier performs 32-bit × 32-bit 2s-complement multiplication with a 64-bit result. The multiplication can be performed with two signed numbers, two unsigned numbers, or one signed number and one unsigned number.

#### 1.3.1 Emulation Logic

The emulation logic is identical to that on the C28x fixed-point CPU. This logic includes the following features. For more details about these features, refer to the *TMS320C28x DSP CPU and Instruction Set Reference Guide* (literature number SPRU430:

- Debug-and-test direct memory access (DT-DMA). A debug host can gain direct access to the content

of registers and memory by taking control of the memory interface during unused cycles of the

instruction pipeline.

- A counter for performance benchmarking.

- Multiple debug events. Any of the following debug events can cause a break in program execution:

- A breakpoint initiated by the ESTOP0 or ESTOP1 instruction.

- An access to a specified program-space or data-space location.

When a debug event causes the C28x to enter the debug-halt state, the event is called a break event.

- Real-time mode of operation.

#### 1.3.2 Memory Map

Like the C28x, the C28x+FPU uses 32-bit data addresses and 22-bit program addresses. This allows for a total address reach of 4G words (1 word = 16 bits) in data space and 4M words in program space. Memory blocks on all C28x+FPU designs are uniformly mapped to both program and data space. For specific details about each of the map segments, see the data sheet for your device.

#### 1.3.3 On-Chip Program and Data

All C28x+FPU based devices contain at least two blocks of single access on-chip memory referred to as M0 and M1. Each of these blocks is 1K words in size. M0 is mapped at addresses 0x0000 – 0x03FF and M1 is mapped at addresses 0x0400 – 0x07FF. Like all other memory blocks on the C28x+FPU devices, M0 and M1 are mapped to both program and data space. Therefore, you can use M0 and M1 to execute code or for data variables. At reset, the stack pointer is set to the top of block M1. Depending on the device, it may also have additional random-access memory (RAM), read-only memory (ROM), external interface zones, or flash memory.

#### 1.3.4 CPU Interrupt Vectors

The C28x+FPU interrupt vectors are identical to those on the C28x CPU. Sixty-four addresses in program space are set aside for a table of 32 CPU interrupt vectors. The CPU vectors can be mapped to the top or bottom of program space by way of the VMAP bit. For more information about the CPU vectors, see *TMS320C28x DSP CPU and Instruction Set Reference Guide* (literature number <u>SPRU430</u>). For devices with a peripheral interrupt expansion (PIE) block, the interrupt vectors will reside in the PIE vector table and this memory can be used as program memory.

#### 1.4 Memory Interface

The C28x+FPU memory interface is identical to that on the C28x. The C28x+FPU memory map is accessible outside the CPU by the memory interface, which connects the CPU logic to memories, peripherals, or other interfaces. The memory interface includes separate buses for program space and data space. This means an instruction can be fetched from program memory while data memory is being accessed. The interface also includes signals that indicate the type of read or write being requested by the CPU. These signals can select a specified memory block or peripheral for a given bus transaction. In addition to 16-bit and 32-bit accesses, the C28x+FPU supports special byte-access instructions that can access the least significant byte (LSByte) or most significant byte (MSByte) of an addressed word. Strobe signals indicate when such an access is occurring on a data bus.

#### 1.4.1 Address and Data Buses

Like the C28x, the memory interface has three address buses:

- **PAB: Program address bus** The PAB carries addresses for reads and writes from program space. PAB is a 22-bit bus.

- DRAB: Data-read address bus

The 32-bit DRAB carries addresses for reads from data space.

- **DWAB: Data-write address bus** The 32-bit DWAB carries addresses for writes to data space.

The memory interface also has three data buses:

- **PRDB: Program-read data bus** The PRDB carries instructions during reads from program space. PRDB is a 32-bit bus.

- DRDB: Data-read data bus The DRDB carries data during reads from data space. DRDB is a 32-bit bus.

- DWDB: Data-/Program-write data bus

The 32-bit DWDB carries data during writes to data space or program space.

A program-space read and a program-space write cannot happen simultaneously because both use the PAB. Similarly, a program-space write and a data-space write cannot happen simultaneously because both use the DWDB. Transactions that use different buses can happen simultaneously. For example, the CPU can read from program space (using PAB and PRDB), read from data space (using DRAB and DRDB), and write to data space (using DWAB and DWDB) at the same time. This behavior is identical to the C28x CPU.

#### 1.4.2 Alignment of 32-Bit Accesses to Even Addresses

The C28x+FPU CPU expects memory wrappers or peripheral-interface logic to align any 32-bit read or write to an even address. If the address-generation logic generates an odd address, the CPU will begin reading or writing at the previous even address. This alignment does not affect the address values generated by the address-generation logic.

Most instruction fetches from program space are performed as 32-bit read operations and are aligned accordingly. However, alignment of instruction fetches are effectively invisible to a programmer. When instructions are stored to program space, they do not have to be aligned to even addresses. Instruction boundaries are decoded within the CPU.

You need to be concerned with alignment when using instructions that perform 32-bit reads from or writes to data space.

Chapter 2 SPRUE02A–June 2007–Revised August 2008

## **CPU Register Set**

The C28x+FPU architecture is the same as the C28x CPU with an extended register and instruction set to support IEEE single-precision floating point operations. This section describes the extensions to the C28x architecture.

| Торіс |               | Page |

|-------|---------------|------|

| 2.1   | CPU Registers | 14   |

#### 2.1 CPU Registers

Devices with the C28x+FPU include the standard C28x register set plus an additional set of floating-point unit registers. The additional floating-point unit registers are the following:

- Eight floating-point result registers, RnH (where n = 0 7)

- Floating-point Status Register (STF)

- Repeat Block Register (RB)

All of the floating-point registers except the repeat block register are shadowed. This shadowing can be used in high priority interrupts for fast context save and restore of the floating-point registers.

Figure 2-1 shows a diagram of both register sets and Table 2-1 shows a register summary. For information on the standard C28x register set, see the *TMS320C28x DSP CPU and Instruction Set Reference Guide* (literature number <u>SPRU430</u>).

| Standard C28x Register Set | Additional 32-bit FPU Registers                   |

|----------------------------|---------------------------------------------------|

| ACC (32-bit)               | R0H (32-bit)                                      |

| P (32-bit)                 |                                                   |

| XT (32-bit)                | R1H (32-bit)                                      |

| XAR0 (32-bit)              | R2H (32-bit)                                      |

| XAR1 (32-bit)              | R3H (32-bit)                                      |

| XAR2 (32-bit)              |                                                   |

| XAR3 (32-bit)              | R4H (32-bit)                                      |

| XAR4 (32-bit)              | R5H (32-bit)                                      |

| XAR5 (32-bit)              |                                                   |

| XAR6 (32-bit)              | R6H (32-bit)                                      |

| XAR7 (32-bit)              | R7H (32-bit)                                      |

| PC (22-bit)                |                                                   |

| RPC (22-bit)               | FPU Status Register (STF)                         |

| DP (16-bit)                | Repeat Block Register (RB)                        |

| SP (16-bit)                | FPU registers R0H - R7H and STF                   |

| ST0 (16 hit)               | are shadowed for fast context<br>save and restore |

| ST0 (16-bit)               |                                                   |

| ST1 (16-bit)               |                                                   |

| IER (16-bit)               |                                                   |

| IFR (16-bit)               |                                                   |

| DBGIER (16-bit)            |                                                   |

#### Figure 2-1. C28x With Floating-Point Registers

| Table 2-1. 28x Plus Floating-Point CPU Register Summar       | v |

|--------------------------------------------------------------|---|

| Tuble E 1. Eox 1 lus 1 louding 1 onit of o Register Ourinnar | y |

| Register | C28x<br>CPU | C28x+FPU | Size    | Description                      | Value After Reset     |

|----------|-------------|----------|---------|----------------------------------|-----------------------|

| ACC      | Yes         | Yes      | 32 bits | Accumulator                      | 0x0000000             |

| AH       | Yes         | Yes      | 16 bits | High half of ACC                 | 0x0000                |

| AL       | Yes         | Yes      | 16 bits | Low half of ACC                  | 0x0000                |

| XAR0     | Yes         | Yes      | 16 bits | Auxiliary register 0             | 0x0000000             |

| XAR1     | Yes         | Yes      | 32 bits | Auxiliary register 1             | 0x0000000             |

| XAR2     | Yes         | Yes      | 32 bits | Auxiliary register 2             | 0x0000000             |

| XAR3     | Yes         | Yes      | 32 bits | Auxiliary register 3             | 0x0000000             |

| XAR4     | Yes         | Yes      | 32 bits | Auxiliary register 4             | 0x0000000             |

| XAR5     | Yes         | Yes      | 32 bits | Auxiliary register 5             | 0x0000000             |

| XAR6     | Yes         | Yes      | 32 bits | Auxiliary register 6             | 0x0000000             |

| XAR7     | Yes         | Yes      | 32 bits | Auxiliary register 7             | 0x0000000             |

| AR0      | Yes         | Yes      | 16 bits | Low half of XAR0                 | 0x0000                |

| AR1      | Yes         | Yes      | 16 bits | Low half of XAR1                 | 0x0000                |

| AR2      | Yes         | Yes      | 16 bits | Low half of XAR2                 | 0x0000                |

| AR3      | Yes         | Yes      | 16 bits | Low half of XAR3                 | 0x0000                |

| AR4      | Yes         | Yes      | 16 bits | Low half of XAR4                 | 0x0000                |

| AR5      | Yes         | Yes      | 16 bits | Low half of XAR5                 | 0x0000                |

| AR6      | Yes         | Yes      | 16 bits | Low half of XAR6                 | 0x0000                |

| AR7      | Yes         | Yes      | 16 bits | Low half of XAR7                 | 0x0000                |

| DP       | Yes         | Yes      | 16 bits | Data-page pointer                | 0x0000                |

| IFR      | Yes         | Yes      | 16 bits | Interrupt flag register          | 0x0000                |

| IER      | Yes         | Yes      | 16 bits | Interrupt enable register        | 0x0000                |

| DBGIER   | Yes         | Yes      | 16 bits | Debug interrupt enable register  | 0x0000                |

| P        | Yes         | Yes      | 32 bits | Product register                 | 0x0000000             |

| PH       | Yes         | Yes      | 16 bits | High half of P                   | 0x0000                |

| PL       | Yes         | Yes      | 16 bits | Low half of P                    | 0x0000                |

| PC       | Yes         | Yes      | 22 bits | Program counter                  | 0x3FFFC0              |

| RPC      | Yes         | Yes      | 22 bits | Return program counter           | 0x0000000             |

| SP       | Yes         | Yes      | 16 bits | Stack pointer                    | 0x0400                |

| ST0      | Yes         | Yes      | 16 bits | Status register 0                | 0x0000                |

| ST1      | Yes         | Yes      | 16 bits | Status register 1                | 0x080B <sup>(1)</sup> |

| хт       | Yes         | Yes      | 32 bits | Multiplicand register            | 0x0000000             |

| т        | Yes         | Yes      | 16 bits | High half of XT                  | 0x0000                |

| TL       | Yes         | Yes      | 16 bits | Low half of XT                   | 0x0000                |

| ROH      | No          | Yes      | 32 bits | Floating-point result register 0 | 0.0                   |

| R1H      | No          | Yes      | 32 bits | Floating-point result register 1 | 0.0                   |

| R2H      | No          | Yes      | 32 bits | Floating-point result register 2 | 0.0                   |

| R3H      | No          | Yes      | 32 bits | Floating-point result register 3 | 0.0                   |

| R4H      | No          | Yes      | 32 bits | Floating-point result register 4 | 0.0                   |

| R5H      | No          | Yes      | 32 bits | Floating-point result register 5 | 0.0                   |

| R6H      | No          | Yes      | 32 bits | Floating-point result register 6 | 0.0                   |

| R7H      | No          | Yes      | 32 bits | Floating-point result register 7 | 0.0                   |

| STF      | No          | Yes      | 32 bits | Floating-point status register   | 0x0000000             |

| RB       | No          | Yes      | 32 bits | Repeat block register            | 0x0000000             |

<sup>(1)</sup> Reset value shown is for devices without the VMAP signal and MOM1MAP signal pinned out. On these devices both of these signals are tied high internal to the device.

#### 2.1.1 Floating-Point Status Register (STF)

The floating-point status register (STF) reflects the results of floating-point operations. There are three basic rules for floating point operation flags:

- 1. Zero and negative flags are set based on moves to registers.

- 2. Zero and negative flags are set based on the result of compare, minimum, maximum, negative and absolute value operations.

- 3. Overflow and underflow flags are set by math instructions such as multiply, add, subtract and 1/x. These flags may also be connected to the peripheral interrupt expansion (PIE) block on your device. This can be useful for debugging underflow and overflow conditions within an application.

As on the C28x, program flow is controlled by C28x instructions that read status flags in the status register 0 (ST0). If a decision needs to be made based on a floating-point operation, the information in the STF register needs to be loaded into ST0 flags (Z,N,OV,TC,C) so that the appropriate branch conditional instruction can be executed. The MOVST0 FLAG instruction is used to load the current value of specified STF flags into the respective bits of ST0. When this instruction executes, it will also clear the latched overflow and underflow flags if those flags are specified.

#### Example 2-1. Moving STF Flags to the ST0 Register

```

Loop:

MOV32 R0H,*XAR4++

MOV32 R1H,*XAR3++

CMPF32 R1H, R0H

MOVST0 ZF, NF ; Move ZF and NF to ST0

BF Loop, GT ; Loop if (R1H > R0H)

```

#### 31 30 16 SHDWS Reserved R/W-0 R-0 15 10 9 8 7 6 5 4 3 2 0 1 Reserved RND32 Reserved TF ΖI NI 7F NF LUF LVF R-0 R/W-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

#### Figure 2-2. Floating-point Unit Status Register (STF)

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 2-2. Floating-point Unit Status (STF) Register Field Descriptions

| Bits    | Field    | Value | Description                                                                                           |

|---------|----------|-------|-------------------------------------------------------------------------------------------------------|

| 31      | SHDWS    |       | Shadow Mode Status Bit                                                                                |

|         |          | 0     | This bit is forced to 0 by the RESTORE instruction.                                                   |

|         |          | 1     | This bit is set to 1 by the SAVE instruction.                                                         |

|         |          |       | This bit is not affected by loading the status register either from memory or from the shadow values. |

| 30 - 10 | Reserved | 0     | Reserved for future use                                                                               |

| 9       | RND32    |       | Round 32-bit Floating-Point Mode                                                                      |

|         |          | 0     | If this bit is zero, the MPYF32, ADDF32 and SUBF32 instructions will round to zero (truncate).        |

|         |          | 1     | If this bit is one, the MPYF32, ADDF32 and SUBF32 instructions will round to the nearest even value.  |

| 8 - 7   | Reserved | 0     | Reserved for future use                                                                               |

#### Table 2-2. Floating-point Unit Status (STF) Register Field Descriptions (continued)

| Bits | Field | Value | Description                                                                                                                                                                                                                                                                                                                                 |

|------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6    | TF    |       | Test Flag                                                                                                                                                                                                                                                                                                                                   |

|      |       |       | The TESTTF instruction can modify this flag based on the condition tested. The SETFLG and SAVE instructions can also be used to modify this flag.                                                                                                                                                                                           |

|      |       | 0     | The condition tested with the TESTTF instruction is false.                                                                                                                                                                                                                                                                                  |

|      |       | 1     | The condition tested with the TESTTF instruction is true.                                                                                                                                                                                                                                                                                   |

| 5    | ZI    |       | Zero Integer Flag                                                                                                                                                                                                                                                                                                                           |

|      |       |       | The following instructions modify this flag based on the integer value stored in the destination register:<br>MOV32, MOVD32, MOVDD32<br>The SETFLG and SAVE instructions can also be used to modify this flag.                                                                                                                              |

|      |       | 0     | The integer value is not zero.                                                                                                                                                                                                                                                                                                              |

|      |       | 1     | The integer value is zero.                                                                                                                                                                                                                                                                                                                  |

| 4    | NI    |       | Negative Integer Flag                                                                                                                                                                                                                                                                                                                       |

|      |       |       | The following instructions modify this flag based on the integer value stored in the destination register:<br>MOV32, MOVD32, MOVDD32<br>The SETFLG and SAVE instructions can also be used to modify this flag.                                                                                                                              |

|      |       | 0     | The integer value is not negative.                                                                                                                                                                                                                                                                                                          |

|      |       | 1     | The integer value is negative.                                                                                                                                                                                                                                                                                                              |

| 3    | ZF    |       | Zero Floating-Point Flag <sup>(1)(2)</sup>                                                                                                                                                                                                                                                                                                  |

| -    |       |       | The following instructions modify this flag based on the floating-point value stored in the destination                                                                                                                                                                                                                                     |

|      |       |       | register:<br>MOV32, MOVD32, MOVDD32, ABSF32, NEGF32<br>The CMPF32, MAXF32, and MINF32 instructions modify this flag based on the result of the operation.<br>The SETFLG and SAVE instructions can also be used to modify this flag                                                                                                          |

|      |       | 0     | The floating-point value is not zero.                                                                                                                                                                                                                                                                                                       |

|      |       | 1     | The floating-point value is zero.                                                                                                                                                                                                                                                                                                           |

| 2    | NF    |       | Negative Floating-Point Flag <sup>(1)(2)</sup>                                                                                                                                                                                                                                                                                              |

|      |       |       | The following instructions modify this flag based on the floating-point value stored in the destination register:<br>MOV32, MOVD32, MOVDD32, ABSF32, NEGF32<br>The CMPF32, MAXF32, and MINF32 instructions modify this flag based on the result of the operation.<br>The SETFLG and SAVE instructions can also be used to modify this flag. |

|      |       | 0     | The floating-point value is not negative.                                                                                                                                                                                                                                                                                                   |

|      |       | 1     | The floating-point value is negative.                                                                                                                                                                                                                                                                                                       |

| 1    | LUF   |       | Latched Underflow Floating-Point Flag                                                                                                                                                                                                                                                                                                       |

|      |       |       | The following instructions will set this flag to 1 if an underflow occurs:<br>MPYF32, ADDF32, SUBF32, MACF32, EINVF32, EISQRTF32                                                                                                                                                                                                            |

|      |       | 0     | An underflow condition has not been latched. If the MOVST0 instruction is used to copy this bit to ST0 then LUF will be cleared.                                                                                                                                                                                                            |

|      |       | 1     | An underflow condition has been latched.                                                                                                                                                                                                                                                                                                    |

| 0    | LVF   |       | Latched Overflow Floating-Point Flag                                                                                                                                                                                                                                                                                                        |

|      |       |       | The following instructions will set this flag to 1 if an overflow occurs:<br>MPYF32, ADDF32, SUBF32, MACF32, EINVF32, EISQRTF32                                                                                                                                                                                                             |

|      |       | 0     | An overflow condition has not been latched. If the MOVST0 instruction is used to copy this bit to ST0, then LVF will be cleared.                                                                                                                                                                                                            |

|      |       | 1     | An overflow condition has been latched.                                                                                                                                                                                                                                                                                                     |

A negative zero floating-point value is treated as a positive zero value when configuring the ZF and NF flags. A DeNorm floating-point value is treated as a positive zero value when configuring the ZF and NF flags. (1)

(2)

CPU Registers

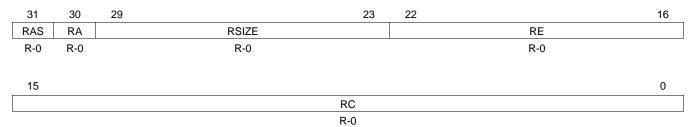

#### 2.1.2 Repeat Block Register (RB)

The repeat block instruction (RPTB) is a new instruction for C28x+FPU. This instruction allows you to repeat a block of code as shown in Example 2-2.

#### Example 2-2. The Repeat Block (RPTB) Instruction uses the RB Register

| ; find the largest element and p<br>MOV32 R0H, *XAR0++; | out its address in XAR6                                   |

|---------------------------------------------------------|-----------------------------------------------------------|

| .align 2                                                | ; Aligns the next instruction to an even address          |

| NOP                                                     | ; Makes RPTB odd aligned - required for a block size of 8 |

| RPTB VECTOR_MAX_END, AR7                                | ; RA is set to 1                                          |

| MOVL ACC, XAR0                                          |                                                           |

| MOV32 R1H,*XAR0++                                       | ; RSIZE reflects the size of the RPTB block               |

| MAXF32 R0H,R1H                                          | ; in this case the block size is 8                        |

| MOVSTO NF, ZF                                           |                                                           |

| MOVL XAR6, ACC, LT                                      |                                                           |

| VECTOR_MAX_END:                                         | ; RE indicates the end address. RA is cleared             |

The C28x\_FPU hardware automatically populates the RB register based on the execution of a RPTB instruction. This register is not normally read by the application and does not accept debugger writes.

#### Figure 2-3. Repeat Block Register (RB)

LEGEND: R = Read only; -n = value after reset

#### Table 2-3. Repeat Block (RB) Register Field Descriptions

| Bits  | Field | Value    | Description                                                                                                                                                                                                                                                                        |

|-------|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | RAS   |          | Repeat Block Active Shadow Bit                                                                                                                                                                                                                                                     |

|       |       |          | When an interrupt occurs the repeat active, RA, bit is copied to the RAS bit and the RA bit is cleared. When an interrupt return instruction occurs, the RAS bit is copied to the RA bit and RAS is cleared.                                                                       |

|       |       | 0        | A repeat block was not active when the interrupt was taken.                                                                                                                                                                                                                        |

|       |       | 1        | A repeat block was active when the interrupt was taken.                                                                                                                                                                                                                            |

| 30    | RA    |          | Repeat Block Active Bit                                                                                                                                                                                                                                                            |

|       |       | 0        | This bit is cleared when the repeat counter, RC, reaches zero.                                                                                                                                                                                                                     |

|       |       |          | When an interrupt occurs the RA bit is copied to the repeat active shadow, RAS, bit and RA is cleared. When an interrupt return, IRET, instruction is executed, the RAS bit is copied to the RA bit and RAS is cleared.                                                            |

|       |       | 1        | This bit is set when the RPTB instruction is executed to indicate that a RPTB is currently active.                                                                                                                                                                                 |

| 29-23 | RSIZE |          | Repeat Block Size                                                                                                                                                                                                                                                                  |

|       |       |          | This 7-bit value specifies the number of 16-bit words within the repeat block. This field is initialized when the RPTB instruction is executed. The value is calculated by the assembler and inserted into the RPTB instruction's RSIZE opcode field.                              |

|       |       | 0-7      | Illegal block size.                                                                                                                                                                                                                                                                |

|       |       | 8/9-0x7F | A RPTB block that starts at an even address must include at least 9 16-bit words and a block that starts at an odd address must include at least 8 16-bit words. The maximum block size is 127 16-bit words. The codegen assembler will check for proper block size and alignment. |

| Table 2-3 | . Repeat Block | (RB) Register Fi | ield Descriptions | (continued) |

|-----------|----------------|------------------|-------------------|-------------|

|           |                | (                |                   | (           |

| Bits  | Field | Value        | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-16 | RE    |              | Repeat Block End Address                                                                                                                                                                                                                                                                                                                                                          |

|       |       |              | This 7-bit value specifies the end address location of the repeat block. The RE value is calculated by hardware based on the RSIZE field and the PC value when the RPTB instruction is executed.                                                                                                                                                                                  |

|       |       |              | RE = lower 7 bits of (PC + 1 + RSIZE)                                                                                                                                                                                                                                                                                                                                             |

| 15-0  | RC    |              | Repeat Count                                                                                                                                                                                                                                                                                                                                                                      |

|       |       | 0            | The block will not be repeated; it will be executed only once. In this case the repeat active, RA, bit will not be set.                                                                                                                                                                                                                                                           |

|       |       | 1-<br>0xFFFF | This 16-bit value determines how many times the block will repeat. The counter is initialized when the RPTB instruction is executed and is decremented when the PC reaches the end of the block. When the counter reaches zero, the repeat active bit is cleared and the block will be executed one more time. Therefore the total number of times the block is executed is RC+1. |

## Pipeline

The pipeline flow for C28x instructions is identical to that of the C28x CPU described in *TMS320C28x DSP CPU and Instruction Set Reference Guide* (SPRU430). Some floating-point instructions, however, use additional execution phases and thus require a delay to allow the operation to complete. This pipeline alignment is achieved by inserting NOPs or non-conflicting instructions when required. Software control of delay slots allows you to improve performance of an application by taking advantage of the delay slots and filling them with non-conflicting instructions. This section describes the key characteristics of the pipeline with regards to floating-point instructions. The rules for avoiding pipeline conflicts are small in number and simple to follow and the C28x+FPU assembler will help you by issuing errors for conflicts.

| Горіс |                                                          |    |  |  |

|-------|----------------------------------------------------------|----|--|--|

|       |                                                          |    |  |  |

| 3.1   | Pipeline Overview                                        | 22 |  |  |

| 3.2   | General Guidelines for Floating-Point Pipeline Alignment | 22 |  |  |

| 3.3   | Moves from FPU Registers to C28x Registers               | 23 |  |  |

| 3.4   | Moves from C28x Registers to FPU Registers               | 23 |  |  |

| 3.5   | Parallel Instructions                                    | 24 |  |  |

| 3.6   | Invalid Delay Instructions                               | 24 |  |  |

| 3.7   | Optimizing the Pipeline                                  | 27 |  |  |

#### 3.1 Pipeline Overview

The C28x FPU pipeline is identical to the C28x pipeline for all standard C28x instructions. In the decode2 stage (D2), it is determined if an instruction is a C28x instruction or a floating-point unit instruction. The pipeline flow is shown in Figure 3-1. Notice that stalls due to normal C28x pipeline stalls (D2) and memory waitstates (R2 and W) will also stall any C28x FPU instruction. Most C28x FPU instructions are single cycle and will complete in the FPU E1 or W stage which aligns to the C28x pipeline. Some instructions will take an additional execute cycle (E2). For these instructions you must wait a cycle for the result from the instruction to be available. The rest of this section will describe when delay cycles are required. Keep in mind that the assembly tools for the C28x+FPU will issue an error if a delay slot has not been handled correctly.

Figure 3-1. FPU Pipeline

#### 3.2 General Guidelines for Floating-Point Pipeline Alignment

While the C28x+FPU assembler will issue errors for pipeline conflicts, you may still find it useful to understand when software delays are required. This section describes three guidelines you can follow when writing C28x+FPU assembly code.

Floating-point instructions that require delay slots have a 'p' after their cycle count. For example '2p' stands for 2 pipelined cycles. This means that an instruction can be started every cycle, but the result of the instruction will only be valid one instruction later.

There are three general guidelines to determine if an instruction needs a delay slot:

- 1. Floating-point math operations (multiply, addition, subtraction, 1/x and MAC) require 1 delay slot.

- 2. Conversion instructions between integer and floating-point formats require 1 delay slot.

- 3. Everything else does not require a delay slot. This includes minimum, maximum, compare, load, store, negative and absolute value instructions.

There are two exceptions to these rules. First, moves between the CPU and FPU registers require special pipeline alignment that is described later in this section. These operations are typically infrequent. Second, the MACF32 R7H, R3H, mem32, \*XAR7 instruction has special requirements that make it easier to use. Refer to the MACF32 instruction description for details.

An example of the 32-bit ADDF32 instruction is shown in Example 3-1. ADDF32 is a 2p instruction and therefore requires one delay slot. The destination register for the operation, R0H, will be updated one cycle after the instruction for a total of 2 cycles. Therefore, a NOP or instruction that does not use R0H must follow this instruction.

Any memory stall or pipeline stall will also stall the floating-point unit. This keeps the floating-point unit aligned with the C28x pipeline and there is no need to change the code based on the waitstates of a memory block.

#### Example 3-1. 2p Instruction Pipeline Alignment

| ADDF32 R0H, #1.5, R1H | ; 2 pipeline cycles (2p)                       |

|-----------------------|------------------------------------------------|

| NOP                   | ; 1 cycle delay or non-conflicting instruction |

|                       | ; < ADDF32 completes, ROH updated              |

| NOP                   | ; Any instruction                              |

#### 3.3 Moves from FPU Registers to C28x Registers

When transferring from the floating-point unit registers to the C28x CPU registers, additional pipeline alignment is required as shown in Example 3-2 and Example 3-3.

Example 3-2. Floating-Point to C28x Register Software Pipeline Alignment

| ;<br>; |              |      | 51    | point minimum: single-cycle operation<br>quired before copying ROH to ACC |

|--------|--------------|------|-------|---------------------------------------------------------------------------|

|        | MINF32       | ROH, | R1H   | ; Single-cycle instruction<br>; < ROH is valid                            |

|        | NOP<br>MOV32 | @ACC | , R0H | ; Alignment cycle<br>; Copy ROH to ACC                                    |

For 1-cycle FPU instructions, one delay slot is required between a write to the floating-point register and the transfer instruction as shown in Example 3-2. For 2p FPU instructions, two delay slots are required between a write to the floating-point register and the transfer instruction as shown in Example 3-3.

#### Example 3-3. Floating-Point to C28x Register Software Pipeline Alignment

| ;; | ADDF32: 32-bit floating-point addition: 2p operation<br>An alignment cycle is required before copying ROH to ACC |       |              |     |                                              |

|----|------------------------------------------------------------------------------------------------------------------|-------|--------------|-----|----------------------------------------------|

|    | ADDF32                                                                                                           | ROH,  | л<br>R1H, #2 | - ; | ROH = R1H + 2, 2 pipeline cycle instruction  |

|    | NOP                                                                                                              |       |              | ;   | 1 delay cycle or non-conflicting instruction |

|    |                                                                                                                  |       |              | ;   | < ROH is valid                               |

|    | NOP                                                                                                              |       |              | ;   | Alignment cycle                              |

|    | MOV32                                                                                                            | @ACC, | ROH          | ;   | Copy ROH to ACC                              |

|    |                                                                                                                  |       |              |     |                                              |

#### 3.4 Moves from C28x Registers to FPU Registers

Transfers from the standard C28x CPU registers to the floating-point registers require four alignment cycles. In this case the four alignment cycles can be filled with NOPs or any non-conflicting instruction except for FRACF32, UI16TOF32, I16TOF32, F32TOUI32, and F32TOI32. These instructions cannot replace any of the four alignment NOPs.

#### Example 3-4. C28x Register to Floating-Point Register Software Pipeline Alignment

```

; Four alignment cycles are required after copying a standard 28x CPU

; register to a floating-point register.

;

MOV32 R0H,@ACC ; Copy ACC to R0H

NOP

NOP

NOP

NOP

NOP

NOP

; Wait 4 cycles

ADDF32 R2H,R1H,R0H ; R0H is valid

```

#### 3.5 Parallel Instructions

Parallel instructions are single opcodes that perform two operations in parallel. This can be a math operation in parallel with a move operation, or two math operations in parallel. Math operations with a parallel move are referred to as 2p/1 instructions. The math portion of the operation takes 2 pipelined cycles while the move portion of the operation is single cycle. This means that NOPs or other non conflicting instructions must be inserted to align the math portion of the operation. An example of an add with parallel move instruction is shown in Example 3-5.

#### Example 3-5. 2p/1 Parallel Instruction Software Pipeline Alignment

```

ADDF32 || MOV32 instruction: 32-bit floating-point add with parallel move

;

ADDF32 is a 2p operation

;

;

MOV32 is a 1 cycle operation

;

ADDF32 R0H, R1H, #2

; ROH = R1H + 2, 2 pipeline cycle operation

|| MOV32 R1H, @Val

; R1H gets the contents of Val, single cycle operation

; <-- MOV32 completes here (R1H is valid)

NOP

; 1 cycle delay or non-conflicting instruction

; <-- ADDF32 completes here (ROH is valid)

NOP

; Any instruction

```

Parallel math instructions are referred to as 2p/2p instructions. Both math operations take 2 cycles to complete. This means that NOPs or other non conflicting instructions must be inserted to align the both math operations. An example of a multiply with parallel add instruction is shown in Example 3-5

#### Example 3-6. 2p/2p Parallel Instruction Software Pipeline Alignment

```

; MPYF32 || ADDF32 instruction: 32-bit floating-point multiply with parallel add

; MPYF32 is a 2p operation

; ADDF32 is a 2p cycle operation

;

MPYF32 ROH, R1H, R3H ; R0H = R1H * R3H, 2 pipeline cycle operation

|| ADDF32 R1H, R2H, R4H ; R1H = R2H + R4H, 2 pipeline cycle operation

NOP ; 1 cycle delay or non-conflicting instruction

; <--- MPYF32 and ADDF32 complete here (R0H and R1H are valid)

NOP ; Any instruction

```

#### 3.6 Invalid Delay Instructions

Most instructions can be used in delay slots as long as source and destination register conflicts are avoided. The C28x+FPU assembler will issue an error anytime you use an conflicting instruction within a delay slot. The following guidelines can be used to avoid these conflicts.

**Note:** Destination register conflicts in delay slots:

Any operation used for pipeline alignment delay must not use the same destination register as the instruction requiring the delay. See Example 3-7.

In Example 3-7 the MPYF32 instruction uses R2H as its destination register. The next instruction should not use R2H as its destination. Since the MOV32 instruction uses the R2H register a pipeline conflict will be issued by the assembler. This conflict can be resolved by using a register other than R2H for the MOV32 instruction as shown in Example 3-8.

#### Example 3-7. Destination Register Conflict

```

; Invalid delay instruction. Both instructions use the same destination register

MPYF32 R2H, R1H, R0H ; 2p instruction

MOV32 R2H, mem32 ; Invalid delay instruction

```

#### Example 3-8. Destination Register Conflict Resolved

```

; Valid delay instruction

MPYF32 R2H, R1H, R0H ; 2p instruction

MOV32 R1H, mem32 ; Valid delay

; <-- MPYF32 completes, R2H valid</pre>

```

**Note:** Instructions in delay slots cannot use the instruction's destination register as a source register.

Any operation used for pipeline alignment delay must not use the destination register of the instruction requiring the delay as a source register as shown in Example 3-9. For parallel instructions, the current value of a register can be used in the parallel operation before it is overwritten as shown in Example 3-11.

In Example 3-9 the MPYF32 instruction again uses R2H as its destination register. The next instruction should not use R2H as its source since the MPYF32 will take an additional cycle to complete. Since the ADDF32 instruction uses the R2H register a pipeline conflict will be issued by the assembler. This conflict can be resolved by using a register other than R2H or by inserting a non-conflicting instruction between the MPYF32 and ADDF32 instructions. Since the SUBF32 does not use R2H this instruction can be moved before the ADDF32 as shown in Example 3-10.

#### Example 3-9. Destination/Source Register Conflict

```

; Invalid delay instruction. ADDF32 should not use R2H as a source operand

MPYF32 R2H, R1H, R0H ; 2p instruction

ADDF32 R3H, R3H, R2H ; Invalid delay instruction

SUBF32 R4H, R1H, R0H

```

#### Example 3-10. Destination/Source Register Conflict Resolved

```

; Valid delay instruction.

MPYF32 R2H, R1H, R0H

SUBF32 R4H, R1H, R0H

ADDF32 R3H, R3H, R2H

NOP

; <-- SUBF32 completes, R4H valid</pre>

```

It should be noted that a source register for the 2nd operation within a parallel instruction can be the same as the destination register of the first operation. This is because the two operations are started at the same time. The 2nd operation is not in the delay slot of the first operation. Consider Example 3-11 where the MPYF32 uses R2H as its destination register. The MOV32 is the 2nd operation in the instruction and can freely use R2H as a source register. The contents of R2H before the multiply will be used by MOV32.

#### Example 3-11. Parallel Instruction Destination/Source Exception

| ; Valid parallel operation. |                                |

|-----------------------------|--------------------------------|

| MPYF32 R2H, R1H, R0H        | ; 2p/1 instruction             |

| MOV32 mem32, R2H            | ; < Uses R2H before the MPYF32 |

|                             | ; < mem32 updated              |

| NOP                         | ; < Delay for MPYF32           |

|                             | ; < R2H updated                |

|                             | -                              |

Likewise, the source register for the 2nd operation within a parallel instruction can be the same as one of the source registers of the first operation. The MPYF32 operation in Example 3-12 uses the R1H register as one of its sources. This register is also updated by the MOV32 register. The multiplication operation will use the value in R1H before the MOV32 updates it.

#### Example 3-12. Parallel Instruction Destination/Source Exception

```

; Valid parallel instruction

MPYF32 R2H, R1H, R0H ; 2p/1 instruction

|| MOV32 R1H, mem32 ; Valid

NOP ; <-- MOV32 completes, R1H valid

; <-- MPYF32, R2H valid</pre>

```

**Note:** Operations within parallel instructions cannot use the same destination register.

When two parallel operations have the same destination register, the result is invalid.

For example, see Example 3-13.

If both operations within a parallel instruction try to update the same destination register as shown in Example 3-13 the assembler will issue an error.

#### Example 3-13. Invalid Destination Within a Parallel Instruction

```

; Invalid parallel instruction. Both operations use the same destination register

MPYF32 R2H, R1H, R0H ; 2p/1 instruction

|| MOV32 R2H, mem32 ; Invalid

```

Some instructions access or modify the STF flags. Because the instruction requiring a delay slot will also be accessing the STF flags, these instructions should not be used in delay slots. These instructions are SAVE, SETFLG, RESTORE and MOVST0.

**Note:** Do not use SAVE, SETFLG, RESTORE, or the MOVST0 instruction in a delay slot.

#### 3.7 Optimizing the Pipeline

The following example shows how delay slots can be used to improve the performance of an algorithm. The example performs two Y = MX+B operations. In Example 3-14, no optimization has been done. The Y = MX+B calculations are sequential and each takes 7 cycles to complete. Notice there are NOPs in the delay slots that could be filled with non-conflicting instructions. The only requirement is these instructions must not cause a register conflict or access the STF register flags.

Example 3-14. Floating-Point Code Without Pipeline Optimization

```

; Using NOPs for alignment cycles, calculate the following:

; Y1 = M1 * X1 + B1

Y2 = M2 * X2 + B2

;

;

; Calculate Y1

NOV32RUH,@M1; Load ROH with M1 - single cycleMOV32R1H,@X1; Load R1H with X1 - single cycleMPYF32R1H,R1H,ROH; R1H = M1 * X1 - 20 cmMOV32R0H,@B1;

;

|| MOV32 R0H,@B1

NOP

; Wait for MPYF32 to complete

; <-- MPYF32 completes, R1H is valid

ADDF32 R1H,R1H,R0H

; R1H = R1H + R0H - 2p operation

NOP

; Wait for ADDF32 to complete

; <-- ADDF32 completes, R1H is valid

MOV32 @Y1,R1H

; Save R1H in Y1

- single cycle

; Calculate Y2

MOV32

ROH,@M2

; Load ROH with M2 - single cycle

MOV32

R1H,@X2

; Load R1H with X2 - single cycle

; R1H = M2 * X2 - 2p operation

; Load R0H with B2 - single cycle

MPYF32 R1H,R1H,R0H

|| MOV32

R0H,@B2

NOP

; Wait for MPYF32 to complete

; <-- MPYF32 completes, R1H is valid

ADDF32 R1H,R1H,R0H

; R1H = R1H + R0H

; Wait for ADDF32 to complete

NOP

; <-- ADDF32 completes, R1H is valid

MOV32 @Y2,R1H

; Save R1H in Y2

; 14 cycles

; 48 bytes

```

The code shown in Example 3-15 was generated by the C28x+FPU compiler with optimization enabled. Notice that the NOPs in the first example have now been filled with other instructions. The code for the two Y = MX+B calculations are now interleaved and both calculations complete in only 9 cycles.

#### Example 3-15. Floating-Point Code With Pipeline Optimization

```

; Using non-conflicting instructions for alignment cycles,

; calculate the following:

; Y1 = M1*X1 + B1

; Y2 = M2 * X2 + B2

MOV32

R2H,@X1

; Load R2H with X1 - single cycle

; Load R1H with M1 - single cycle

MOV32

R1H,@M1

; R3H = M1 * X1 - 2p operation

; Load R0H with M2 - single cycle

MPYF32

R3H,R2H,R1H

ROH,@M2

MOV32

; Load R1H with X2 - single cycle

MOV32

R1H,@X2

; <-- MPYF32 completes, R3H is valid

; ROH = M2 * X2

MPYF32

ROH,R1H,ROH

- 2p operation

|| MOV32

R4H,@B1

; Load R4H with B1 - single cycle

; <-- MOV32 completes, R4H is valid

; R1H = B1 + M1*X1 - 2p operation

; Load R2H with B2 - single cycle

ADDF32

R1H,R4H,R3H

|| MOV32

R2H,@B2

; <-- MPYF32 completes, ROH is valid

; R0H = B2 + M2\timesZ - 2p operation

ADDF32

ROH,R2H,ROH

; <-- ADDF32 completes, R1H is valid

MOV32

@Y1,R1H

; Store Y1

; <-- ADDF32 completes, ROH is valid

MOV32

@Y2,R0H

; Store Y2

;

9 cycles

; 36 bytes

```

28

### **Instruction Set**

This chapter describes the assembly language instructions of the TMS320C28x plus floating-point processor. Also described are parallel operations, conditional operations, resource constraints, and addressing modes. The instructions listed here are an extension to the standard C28x instruction set. For information on standard C28x instructions, see the *TMS320C28x DSP CPU and Instruction Set Reference Guide* (literature number SPRU430).

| Торіс      |                          | Page |

|------------|--------------------------|------|

| 4.1<br>4.2 | Instruction Descriptions |      |

#### 4.1 Instruction Descriptions

This section gives detailed information on the instruction set. Each instruction may present the following information:

- Operands

- Opcode

- Description

- Exceptions

- Pipeline

- Examples

- See also

The example INSTRUCTION is shown to familiarize you with the way each instruction is described. The example describes the kind of information you will find in each part of the individual instruction description and where to obtain more information. On the C28x+FPU instructions, follow the same format as the C28x. The source operand(s) are always on the right and the destination operand(s) are on the left.

The explanations for the syntax of the operands used in the instruction descriptions for the TMS320C28x plus floating-point processor are given in Table 4-1. For information on the operands of standard C28x instructions, see the TMS320C28x DSP CPU and Instruction Set Reference Guide (SPRU430).