# 2.2 Registers

| Addr.        | Register Name                        |                 | Bit 7 | 6          | 5      | 4     | 3          | 2      | 1           | Bit 0 |

|--------------|--------------------------------------|-----------------|-------|------------|--------|-------|------------|--------|-------------|-------|

| \$0000       | Port A Data Register<br>(PORTA)      | Read:<br>Write: | PA7   | PA6        | PA5    | PA4   | PA3        | PA2    | PA1         | PA0   |

|              | See page 88.                         | Reset:          | U     | U          | U      | U     | U          | U      | U           | U     |

| \$0001       | Port B Data Register<br>(PORTB)      | Read:<br>Write: | PB7   | PB6        | PB5    | PB4   | PB3        | PB2    | PB1         | PB0   |

|              | See page 89.                         | Reset:          | U     | U          | U      | U     | U          | U      | U           | U     |

| \$0002       | Data Direction Register A (DDRA)     | Read:<br>Write: | DDA7  | DDA6       | DDA5   | DDA4  | DDA3       | DDA2   | DDA1        | DDA0  |

|              | See page 89.                         | Reset:          | 0     | 0          | 0      | 0     | 0          | 0      | 0           | 0     |

| \$0003       | Data Direction Register B (DDRB)     | Read:<br>Write: | DDB7  | DDB6       | DDB5   | DDB4  | DDB3       | DDB2   | DDB1        | DDB0  |

|              | See page 90.                         | Reset:          | 0     | 0          | 0      | 0     | 0          | 0      | 0           | 0     |

| \$0004       | Reserved                             |                 | R     | R          | R      | R     | R          | R      | R           | R     |

| $\downarrow$ |                                      |                 |       |            |        |       |            |        |             |       |

| \$0007       | Reserved                             |                 | R     | R          | R      | R     | R          | R      | R           | R     |

| \$0008       | Port E Data Register<br>(PORTE)      | Read:<br>Write: | PE7   | PE6        | PE5    | PD4   | PD3        | PD2    | PD1         | PD0   |

|              | See page 90.                         | Reset:          | 0     | 0          | 0      | 0     | 0          | 0      | 0           | 0     |

| \$0009       | Data Direction Register E<br>(DDRE)  | Read:<br>Write: | DDE7  | DDE6       | DDE5   | DDE4  | DDE3       | DDE2   | 0           | 0     |

|              | See page 91.                         | Reset:          | 0     | 0          | 0      | 0     | 1          | 0      | 0           | 0     |

| \$000A       | Port E Assignment Register<br>(PEAR) | Read:<br>Write: | NDBE  | CGMTE      | PIPOE  | NECLK | LSTRE      | RDWE   | 0           | 0     |

|              | See page 92.                         | Reset:          | 1     | 0          | 0      | 1     | 0          | 0      | 0           | 0     |

| \$000B       | Mode Register<br>(MODE)              | Read:<br>Write: | SMODN | MODB       | MODA   | ESTR  | IVIS       | EBSWAI | 0           | EME   |

|              | See page 81.                         | Reset:          | 0     | 0          | 0      | 1     | 1          | 0      | 0           | 1     |

| \$000C       | Pullup Control Register (PUCR)       | Read:<br>Write: | 0     | 0          | 0      | PUPE  | 0          | 0      | PUPB        | PUPA  |

|              | See page 94.                         | Reset:          | 0     | 0          | 0      | 1     | 0          | 0      | 0           | 0     |

|              | Reduced Drive Register               | Read:           | 0     | 0          | 0      | 0     | RDPE       | 0      | RDPB        | RDPA  |

| \$000D       | (RDRIV)                              | Write:          |       |            |        |       | INDE       |        | ווטרט       | INDEX |

|              | See page 95.                         | Reset:          | 0     | 0          | 0      | 0     | 0          | 0      | 0           | 0     |

| \$000E       | Reserved                             |                 | R     | R          | R      | R     | R          | R      | R           | R     |

| <b>N</b> 1 . |                                      |                 |       | = Unimplen | nented | R     | = Reserved |        | U = Unaffec | ted   |

## Notes:

- 1. Available only on MC68HC912B32 and MC68HC912BC32 devices.

- 2. Available only on MC68HC912B32 and MC68HC12BE32 devices.

- 3. Available only on MC68HC(9)12BC32 devices.

Figure 2-1. Register Map (Sheet 1 of 19)

Data Sheet M68HC12B Family — Rev. 8.0

| Addr.    | Register Name                                    |                 | Bit 7 | 6          | 5      | 4      | 3          | 2      | 1           | Bit 0  |

|----------|--------------------------------------------------|-----------------|-------|------------|--------|--------|------------|--------|-------------|--------|

| \$000F   | Reserved                                         |                 | R     | R          | R      | R      | R          | R      | R           | R      |

| \$0010   | RAM Initialization Register (INITRM)             | Read:<br>Write: | RAM15 | RAM14      | RAM13  | RAM12  | RAM11      | 0      | 0           | 0      |

|          | See page 83.                                     | Reset:          | 0     | 0          | 0      | 0      | 1          | 0      | 0           | 0      |

| \$0011   | Register Initialization Register (INITRG)        | Read:<br>Write: | REG15 | REG14      | REG13  | REG12  | REG11      | 0      | 0           | MMSWAI |

|          | See page 82.                                     | Reset:          | 0     | 0          | 0      | 0      | 0          | 0      | 0           | 0      |

| \$0012   | EEPROM Initialization Register (INITEE)          | Read:<br>Write: | EE15  | EE14       | EE13   | EE12   | 0          | 0      | 0           | EEON   |

|          | See page 83.                                     | Reset:          | 0     | 0          | 0      | 1      | 0          | 0      | 0           | 1      |

| \$0013   | Miscellaneous Mapping Control<br>Register (MISC) | Read:<br>Write: | 0     | NDRF       | RFSTR1 | RFSTR0 | EXSTR1     | EXSTR0 | MAPROM      | ROMON  |

|          | See page 84.                                     | Reset:          | 0     | 0          | 0      | 0      | 0          | 0      | 0           | 0      |

| \$0014   | Real-Time Interrupt Control<br>Register (RTICTL) | Read:<br>Write: | RTIE  | RSWAI      | RSBCK  | 0      | RTBYP      | RTR2   | RTR1        | RTR0   |

|          | See page 124.                                    | Reset:          | 0     | 0          | 0      | 0      | 0          | 0      | 0           | 0      |

| \$0015   | Real-Time Interrupt Flag Register (RTIFLG)       | Read:<br>Write: | RTIF  | 0          | 0      | 0      | 0          | 0      | 0           | 0      |

|          | See page 125.                                    | Reset:          | 0     | 0          | 0      | 0      | 0          | 0      | 0           | 0      |

| \$0016   | COP Control Register (COPCTL)                    | Read:<br>Write: | CME   | FCME       | FCM    | FCOP   | DISR       | CR2    | CR1         | CR0    |

|          | See page 125.                                    | Reset:          | 0     | 0          | 0      | 0      | 0          | 0      | 0           | 1      |

| \$0017   | Arm/Reset COP Timer<br>Register (COPRST)         | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0  |

|          | See page 127.                                    | Reset:          | 0     | 0          | 0      | 0      | 0          | 0      | 0           | 0      |

| \$0018   | Reserved                                         |                 | R     | R          | R      | R      | R          | R      | R           | R      |

| <b>↓</b> |                                                  | Г               |       |            |        |        |            |        |             |        |

| \$001D   | Reserved                                         |                 | R     | R          | R      | R      | R          | R      | R           | R      |

| \$001E   | Interrupt Control Register (INTCR)               | Read:<br>Write: | IRQE  | IRQEN      | DLY    | 0      | 0          | 0      | 0           | 0      |

|          | See page 72.                                     | Reset:          | 0     | 1          | 1      | 0      | 0          | 0      | 0           | 0      |

| \$001F   | Highest Priority I Interrupt Register (HPRIO)    | Read:<br>Write: | 1     | 1          | PSEL5  | PSEL4  | PSEL3      | PSEL2  | PSEL1       | 0      |

|          | See page 73.                                     | Reset:          | 1     | 1          | 1      | 1      | 0          | 0      | 1           | 0      |

|          |                                                  |                 |       | = Unimplen | nented | R      | = Reserved |        | U = Unaffec | ted    |

- Available only on MC68HC912B32 and MC68HC912BC32 devices.

Available only on MC68HC912B32 and MC68HC12BE32 devices.

Available only on MC68HC(9)12BC32 devices.

Figure 2-1. Register Map (Sheet 2 of 19)

| Addr.        | Register Name                                     |                 | Bit 7  | 6          | 5      | 4      | 3          | 2      | 1           | Bit 0    |

|--------------|---------------------------------------------------|-----------------|--------|------------|--------|--------|------------|--------|-------------|----------|

| \$0020       | Breakpoint Control Register 0<br>(BRKCT0)         | Read:<br>Write: | BKEN1  | BKEN0      | BKPM   | 0      | BK1ALE     | BK0ALE | 0           | 0        |

|              | See page 329.                                     | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0        |

| \$0021       | Breakpoint Control Register 1 (BRKCT1)            | Read:<br>Write: | 0      | BKDBE      | ВКМВН  | BKMBL  | BK1RWE     | BK1RW  | BK0RWE      | BK0RW    |

|              | See page 330.                                     | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0        |

| \$0022       | Breakpoint Address Register High (BRKAH)          | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9       | Bit 8    |

|              | See page 332.                                     | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0        |

| \$0023       | Breakpoint Address Register Low (BRKAL)           | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0    |

|              | See page 332.                                     | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0        |

| \$0024       | Breakpoint Data Register High<br>(BRKDH)          | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9       | Bit 8    |

|              | See page 332.                                     | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0        |

| \$0025       | Breakpoint Data Register Low (BRKDL)              | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0    |

|              | See page 333.                                     | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0        |

| \$0026       | Reserved                                          |                 | R      | R          | R      | R      | R          | R      | R           | R        |

| $\downarrow$ |                                                   |                 |        |            |        |        |            |        |             |          |

| \$003F       | Reserved                                          |                 | R      | R          | R      | R      | R          | R      | R           | R        |

| \$0040       | PWM Clocks and Concatenate<br>Register (PWCLK)    | Read:<br>Write: | CON23  | CON01      | PCKA2  | PCKA1  | PCKA0      | PCKB2  | PCKB1       | PCKB0    |

|              | See page 135.                                     | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0        |

| \$0041       | PWM Clock Select and Polarity<br>Register (PWPOL) | Read:<br>Write: | PCLK3  | PCLK2      | PCLK1  | PCLK0  | PPOL3      | PPOL2  | PPOL1       | PPOL0    |

|              | See page 136.                                     | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0        |

|              | PWM Enable Register                               | Read:           | 0      | 0          | 0      | 0      | PWEN3      | PWEN2  | PWEN1       | PWEN0    |

| \$0042       | (PWEN)                                            | Write:          |        |            |        |        | 1 112110   |        |             | 1 112110 |

|              | See page 138.                                     | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0        |

| \$0043       | PWM Prescaler Counter Register (PWPRES)           | Read:<br>Write: | 0      | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0    |

|              | See page 139.                                     | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0        |

| \$0044       | PWM Scale Register 0<br>(PWSCAL0)                 | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0    |

|              | See page 139.                                     | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0        |

| <b>N</b> 1 . |                                                   |                 |        | = Unimplen | nented | R      | = Reserved |        | U = Unaffec | ted      |

**Data Sheet**

- 1. Available only on MC68HC912B32 and MC68HC912BC32 devices.

- 2. Available only on MC68HC912B32 and MC68HC12BE32 devices.

- 3. Available only on MC68HC(9)12BC32 devices.

Figure 2-1. Register Map (Sheet 3 of 19)

| Addr.        | Register Name                                   |                 | Bit 7 | 6          | 5      | 4     | 3          | 2     | 1           | Bit 0 |

|--------------|-------------------------------------------------|-----------------|-------|------------|--------|-------|------------|-------|-------------|-------|

|              | PWM Scale Counter Register 0                    | Read:           | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

| \$0045       | (PWSCNT0)                                       | Write:          |       |            |        |       |            |       |             |       |

|              | See page 139.                                   | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0046       | PWM Scale Register 1 (PWSCAL1)<br>See page 140. | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|              | ooo pago : ioi                                  | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

|              | PWM Scale Counter Register 1                    | Read:           | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

| \$0047       | (PWSCNT1)                                       | Write:          |       |            |        |       |            |       |             |       |

|              | See page 140.                                   | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0048       | PWM Channel Counter Register 0 (PWCNT0)         | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|              | See page 141.                                   | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0049       | PWM Channel Counter Register 1 (PWCNT1)         | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|              | See page 141.                                   | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$004A       | PWM Channel Counter Register 2 (PWCNT2)         | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|              | See page 141.                                   | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$004B       | PWM Channel Counter Register 3 (PWCNT3)         | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|              | See page 141.                                   | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$004C       | PWM Channel Period Register 0 (PWPER0)          | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|              | See page 142.                                   | Reset:          | 1     | 1          | 1      | 1     | 1          | 1     | 1           | 1     |

| \$004D       | PWM Channel Period Register 1 (PWPER1)          | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|              | See page 142.                                   | Reset:          | 1     | 1          | 1      | 1     | 1          | 1     | 1           | 1     |

| \$004E       | PWM Channel Period Register 2 (PWPER2)          | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|              | See page 142.                                   | Reset:          | 1     | 1          | 1      | 1     | 1          | 1     | 1           | 1     |

| \$004F       | PWM Channel Period Register 3 (PWPER3)          | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|              | See page 142.                                   | Reset:          | 1     | 1          | 1      | 1     | 1          | 1     | 1           | 1     |

| \$0050       | PWM Channel Duty Register 0<br>(PWDTY0)         | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|              | See page 143.                                   | Reset:          | 1     | 1          | 1      | 1     | 11         | 1     | 1           | 1     |

| <b>N</b> 1 ( |                                                 |                 |       | = Unimpler | nented | R     | = Reserved |       | U = Unaffec | ted   |

- Available only on MC68HC912B32 and MC68HC912BC32 devices.

Available only on MC68HC912B32 and MC68HC12BE32 devices.

Available only on MC68HC(9)12BC32 devices.

Figure 2-1. Register Map (Sheet 4 of 19)

| Addr.        | Register Name                           |                 | Bit 7 | 6          | 5      | 4     | 3          | 2     | 1           | Bit 0 |

|--------------|-----------------------------------------|-----------------|-------|------------|--------|-------|------------|-------|-------------|-------|

| \$0051       | PWM Channel Duty Register 1<br>(PWDTY1) | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|              | See page 143.                           | Reset:          | 1     | 1          | 1      | 1     | 1          | 1     | 1           | 1     |

| \$0052       | PWM Channel Duty Register 2<br>(PWDTY2) | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|              | See page 143.                           | Reset:          | 1     | 1          | 1      | 1     | 1          | 1     | 1           | 1     |

| \$0053       | PWM Channel Duty Register 3 (PWDTY3)    | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|              | See page 143.                           | Reset:          | 1     | 1          | 1      | 1     | 1          | 1     | 1           | 1     |

| \$0054       | PWM Control Register (PWCTL)            | Read:<br>Write: | 0     | 0          | 0      | PSWAI | CENTR      | RDPP  | PUPP        | PSBCK |

|              | See page 144.                           | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

|              | PWM Special Mode Register               | Read:           | DISCR | DISCP      | DISCAL | 0     | 0          | 0     | 0           | 0     |

| \$0055       | (PWTST)                                 | Write:          | DIOON | Diooi      |        |       |            |       |             |       |

|              | See page 145.                           | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0056       | Port P Data Register<br>(PORTP)         | Read:<br>Write: | PP7   | PP6        | PP5    | PP4   | PP3        | PP2   | PP1         | PP0   |

|              | See page 145.                           | Reset:          | U     | U          | U      | U     | U          | U     | U           | U     |

| \$0057       | Port P Data Direction Register (DDRP)   | Read:<br>Write: | DDP7  | DDP6       | DDP5   | DDP4  | DDP3       | DDP2  | DDP1        | DDP0  |

|              | See page 146.                           | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0058       | Reserved                                |                 | R     | R          | R      | R     | R          | R     | R           | R     |

| $\downarrow$ |                                         | •               |       |            |        |       |            |       |             |       |

| \$005F       | Reserved                                |                 | R     | R          | R      | R     | R          | R     | R           | R     |

| \$0060       | ATD Control Register 0<br>(ATDCTL0)     | Read:<br>Write: | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

|              | See page 303.                           | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0061       | ATD Control Register 1<br>(ATDCTL1)     | Read:<br>Write: | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

|              | See page 303.                           | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0062       | ATD Control Register 2<br>(ATDCTL2)     | Read:<br>Write: | ADPU  | AFFC       | AWAI   | 0     | 0          | 0     | ASCIE       | ASCIF |

|              | See page 303.                           | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0063       | ATD Control Register 3 (ATDCTL3)        | Read:<br>Write: | 0     | 0          | 0      | 0     | 0          | 0     | FRZ1        | FRZ0  |

|              | See page 304.                           | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

|              |                                         |                 |       | = Unimplen | nented | R     | = Reserved |       | U = Unaffec | ted   |

|              |                                         |                 |       | ı '        |        |       | J          |       |             |       |

**Data Sheet**

- 1. Available only on MC68HC912B32 and MC68HC912BC32 devices.

2. Available only on MC68HC912B32 and MC68HC12BE32 devices.

- 3. Available only on MC68HC(9)12BC32 devices.

Figure 2-1. Register Map (Sheet 5 of 19)

| Addr.        | Register Name                           |                 | Bit 7  | 6          | 5         | 4               | 3            | 2          | 1           | Bit 0 |

|--------------|-----------------------------------------|-----------------|--------|------------|-----------|-----------------|--------------|------------|-------------|-------|

| \$0064       | ATD Control Register 4<br>(ATDCTL4)     | Read:<br>Write: | S10BM  | SMP1       | SMP0      | PRS4            | PRS3         | PRS2       | PRS1        | PRS0  |

|              | See page 305.                           | Reset:          | 0      | 0          | 0         | 0               | 0            | 0          | 0           | 1     |

| \$0065       | ATD Control Register 5<br>(ATDCTL5)     | Read:<br>Write: |        | S8CM       | SCAN      | MULT            | CD           | CC         | СВ          | CA    |

|              | See page 307.                           | Reset:          | 0      | 0          | 0         | 0               | 0            | 0          | 0           | 0     |

|              | ATD Status Register                     | Read:           | SCF    | 0          | 0         | 0               | 0            | CC2        | CC1         | CC0   |

| \$0066       | (ATDSTAT)                               | Write:          |        |            |           |                 |              |            |             |       |

|              | See page 309.                           | Reset:          | 0      | 0          | 0         | 0               | 0            | 0          | 0           | 0     |

|              | ATD Status Register                     | Read:           | CCF7   | CCF6       | CCF5      | CCF4            | CCF3         | CCF2       | CCF1        | CCF0  |

| \$0067       | (ATDSTAT)                               | Write:          |        |            |           |                 |              |            |             |       |

|              | See page 309.                           | Reset:          | 0      | 0          | 0         | 0               | 0            | 0          | 0           | 0     |

| \$0068       | ATD Test Register High<br>(ATDTSTH)     | Read:<br>Write: | SAR9   | SAR8       | SAR7      | SAR6            | SAR5         | SAR4       | SAR3        | SAR2  |

|              | See page 310.                           | Reset:          | 0      | 0          | 0         | 0               | 0            | 0          | 0           | 0     |

| \$0069       | ATD Test Register Low (ATDTSTL)         | Read:<br>Write: | SAR1   | SAR0       | RST       | TSTOUT          | TST3         | TST2       | TST1        | TST0  |

|              | See page 310.                           | Reset:          | 0      | 0          | 0         | 0               | 0            | 0          | 0           | 0     |

| \$006A       | Reserved                                |                 | R      | R          | R         | R               | R            | R          | R           | R     |

| $\downarrow$ |                                         |                 |        |            |           |                 |              |            |             |       |

| \$006E       | Reserved                                |                 | R      | R          | R         | R               | R            | R          | R           | R     |

| \$006F       | Port AD Data Input Register<br>(PORTAD) | Read:<br>Write: | PAD7   | PAD6       | PAD5      | PAD4            | PAD3         | PAD2       | PAD1        | PAD0  |

|              | See page 311.                           | Reset:          |        |            | After res | et, reflect the | state of the | input pins |             |       |

|              | ATD Result Register 0                   | Read:           | Bit 15 | Bit 14     | Bit 13    | Bit 12          | Bit 11       | Bit 10     | Bit 9       | Bit 8 |

| \$0070       | (ADRx0H)                                | Write:          |        |            |           |                 |              |            |             |       |

|              | See page 311.                           | Reset:          |        |            |           | Unde            | fined        |            |             |       |

|              | ATD Result Register 0                   | Read:           | Bit 7  | Bit 6      | Bit 5     | Bit 4           | Bit 3        | Bit 2      | Bit 1       | Bit 0 |

| \$0071       | (ADRx0L)                                | Write:          |        |            |           |                 |              |            |             |       |

|              | See page 312.                           | Reset:          |        | T          | ı         | Unde            |              | ı          | ı           |       |

|              | ATD Result Register 1                   |                 | Bit 15 | Bit 14     | Bit 13    | Bit 12          | Bit 11       | Bit 10     | Bit 9       | Bit 8 |

| \$0072       | (ADRx1H)                                | Write:          |        |            |           |                 |              |            |             |       |

|              | See page 312.                           | Reset:          |        | T          | ı         | Unde            |              | 1          | 1           |       |

|              | ATD Result Register 1                   | Read:           | Bit 7  | Bit 6      | Bit 5     | Bit 4           | Bit 3        | Bit 2      | Bit 1       | Bit 0 |

| \$0073       | (ADRx1L)                                | Write:          |        |            |           |                 |              |            |             |       |

|              | See page 312.                           | Reset:          |        | 1          |           | Unde            | i e          |            |             |       |

| Notes:       |                                         |                 |        | = Unimplen | nented    | R               | = Reserved   |            | U = Unaffec | ted   |

- Available only on MC68HC912B32 and MC68HC912BC32 devices.

Available only on MC68HC912B32 and MC68HC12BE32 devices.

Available only on MC68HC(9)12BC32 devices.

Figure 2-1. Register Map (Sheet 6 of 19)

M68HC12B Family — Rev. 8.0

| Addr.         | Register Name             |        | Bit 7  | 6          | 5      | 4      | 3          | 2              | 1           | Bit 0 |

|---------------|---------------------------|--------|--------|------------|--------|--------|------------|----------------|-------------|-------|

|               | ATD Result Register 2     | Read:  | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10         | Bit 9       | Bit 8 |

| \$0074        | (ADRx2H)                  | Write: |        |            |        |        |            |                |             |       |

|               | See page 312.             | Reset: |        |            |        | Unde   | efined     |                |             |       |

|               | ATD Result Register 2     | Read:  | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2          | Bit 1       | Bit 0 |

| \$0075        | (ADRx2L)                  | Write: |        |            |        |        |            |                |             |       |

|               | See page 312.             | Reset: |        |            |        | Unde   | efined     |                |             |       |

|               | ATD Result Register 3     | Read:  | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10         | Bit 9       | Bit 8 |

| \$0076        | (ADRx3H)                  | Write: |        |            |        |        |            |                |             |       |

|               | See page 312.             | Reset: |        |            |        | Unde   | fined      |                |             |       |

|               | ATD Result Register 3     | Read:  | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2          | Bit 1       | Bit 0 |

| \$0077        | (ADRx3L)                  | Write: |        |            |        |        |            |                |             |       |

|               | See page 312.             | Reset: |        |            |        | Unde   |            |                |             |       |

|               | ATD Result Register 4     | Read:  | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10         | Bit 9       | Bit 8 |

| \$0078        | (ADRx4H)                  | Write: |        |            |        |        |            |                |             |       |

|               | See page 312.             | Reset: |        |            |        | Unde   |            |                |             |       |

|               | ATD Result Register 4     | Read:  | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2          | Bit 1       | Bit 0 |

| \$0079        | (ADRx4L)                  | Write: |        |            |        |        |            |                |             |       |

|               | See page 312.             | Reset: |        | ,          | ı      | Unde   |            |                | ,           | ,     |

|               | ATD Result Register 5     | Read:  | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10         | Bit 9       | Bit 8 |

| \$007A        | (ADRx5H)                  | Write: |        |            |        |        |            |                |             |       |

|               | See page 312.             | Reset: |        | T          | T      | Unde   |            |                | T           |       |

|               | ATD Result Register 5     | Read:  | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2          | Bit 1       | Bit 0 |

| \$007B        | (ADRx5L)<br>See page 312. | Write: |        |            |        |        |            |                |             |       |

|               | See page 312.             | Reset: |        |            | I      | Unde   |            |                |             |       |

|               | ATD Result Register 6     | Read:  | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10         | Bit 9       | Bit 8 |

| \$007C        | (ADRx6H)<br>See page 312. | Write: |        |            |        |        |            |                |             |       |

|               | 3ee page 312.             | Reset: |        | T =::-     | I      | Unde   |            | <b></b>        |             |       |

| <b>****</b>   | ATD Result Register 6     | Read:  | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2          | Bit 1       | Bit 0 |

| \$007D        | (ADRx6L)<br>See page 312. | Write: |        |            |        |        | <u> </u>   |                |             |       |

|               |                           | Reset: |        |            |        | Unde   |            | <b>5</b> 11.15 | T =::-      |       |

| <b>-</b>      | ATD Result Register 7     | Read:  | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10         | Bit 9       | Bit 8 |

| \$007E        | (ADRx7H)<br>See page 312. | Write: |        |            |        |        | <u> </u>   |                |             |       |

|               |                           | Reset: |        | T =::-     | I      | Unde   |            | <b></b>        |             |       |

| <b>#</b> 00== | ATD Result Register 7     | Read:  | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2          | Bit 1       | Bit 0 |

| \$007F        | (ADRx7L)<br>See page 312. | Write: |        |            |        |        | f:I        |                |             |       |

|               | Gee page 312.             | Reset: |        | 1          |        | Unde   |            |                |             |       |

| <b>N</b> 1 4  |                           |        |        | = Unimpler | nented | R      | = Reserved |                | U = Unaffec | ted   |

- 1. Available only on MC68HC912B32 and MC68HC912BC32 devices.

2. Available only on MC68HC912B32 and MC68HC12BE32 devices.

- 3. Available only on MC68HC(9)12BC32 devices.

Figure 2-1. Register Map (Sheet 7 of 19)

**Data Sheet** M68HC12B Family — Rev. 8.0

| Addr.  | Register Name                                  |                 | Bit 7  | 6          | 5      | 4      | 3          | 2      | 1           | Bit 0 |

|--------|------------------------------------------------|-----------------|--------|------------|--------|--------|------------|--------|-------------|-------|

| \$0080 | Timer IC/OC Select Register (TIOS)             | Read:<br>Write: | IOS7   | IOS6       | IOS5   | IOS4   | IOS3       | IOS2   | IOS1        | IOS0  |

|        | See page 151.                                  | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0081 | Timer Compare Force Register (CFORC)           | Read:<br>Write: | FOC7   | FOC6       | FOC5   | FOC4   | FOC3       | FOC2   | FOC1        | FOC0  |

|        | See page 151.                                  | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0082 | Timer Output Compare 7 Mask<br>Register (OC7M) | Read:<br>Write: | OC7M7  | OC7M6      | OC7M5  | OC7M4  | ОС7М3      | OC7M2  | OC7M1       | ОС7М0 |

|        | See page 152.                                  | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0083 | Timer Output Compare 7 Data<br>Register (OC7D) | Read:<br>Write: | OC7D7  | OC7D6      | OC7D5  | OC7D4  | OC7D3      | OC7D2  | OC7D1       | OC7D0 |

|        | See page 152.                                  | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

|        | Timer Count Register High                      | Read:           | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9       | Bit 8 |

| \$0084 | (TCNTH)                                        | Write:          |        |            |        |        |            |        |             |       |

|        | See page 153.                                  | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

|        | Timer Count Register Low                       | Read:           | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

| \$0085 | (TCNTL)                                        | Write:          |        |            |        |        |            |        |             |       |

|        | See page 153.                                  | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0086 | Timer System Control Register (TSCR)           | Read:<br>Write: | TEN    | TSWAI      | TSBCK  | TFFCA  |            |        |             |       |

|        | See page 153.                                  | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0087 | Reserved                                       |                 | R      | R          | R      | R      | R          | R      | R           | R     |

| \$0088 | Timer Control Register 1 (TCTL1)               | Read:<br>Write: | OM7    | OL7        | OM6    | OL6    | OM5        | OL5    | OM4         | OL4   |

|        | See page 154.                                  | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0089 | Timer Control Register 2<br>(TCTL2)            | Read:<br>Write: | ОМЗ    | OL3        | OM2    | OL2    | OM1        | OL1    | ОМ0         | OL0   |

|        | See page 154.                                  | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$008A | Timer Control Register 3<br>(TCTL3)            | Read:<br>Write: | EDG7B  | EDG7A      | EDG6B  | EDG6A  | EDG5B      | EDG5A  | EDG4B       | EDG4A |

|        | See page 155.                                  | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$008B | Timer Control Register 4<br>(TCTL4)            | Read:<br>Write: | EDG3B  | EDG3A      | EDG2B  | EDG2A  | EDG1B      | EDG1A  | EDG0B       | EDG0A |

|        | See page 155.                                  | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

|        |                                                |                 |        | = Unimplen | nented | R      | = Reserved |        | U = Unaffec | ted   |

- Available only on MC68HC912B32 and MC68HC912BC32 devices.

Available only on MC68HC912B32 and MC68HC12BE32 devices.

Available only on MC68HC(9)12BC32 devices.

Figure 2-1. Register Map (Sheet 8 of 19)

| Addr.        | Register Name                                                                 |                 | Bit 7  | 6          | 5      | 4      | 3          | 2      | 1           | Bit 0 |

|--------------|-------------------------------------------------------------------------------|-----------------|--------|------------|--------|--------|------------|--------|-------------|-------|

| \$008C       | Timer Mask Register 1<br>(TMSK1)                                              | Read:<br>Write: | C7I    | C6I        | C5I    | C4I    | C3I        | C2I    | C1I         | COI   |

|              | See page 156.                                                                 | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$008D       | Timer Mask Register 2<br>(TMSK2)                                              | Read:<br>Write: | TOI    | 0          | PUPT   | RDPT   | TCRE       | PR2    | PR1         | PR0   |

|              | See page 156.                                                                 | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$008E       | Timer Interrupt Flag Register 1<br>(TFLG1)                                    | Read:<br>Write: | C7F    | C6F        | C5F    | C4F    | C3F        | C2F    | C1F         | C0F   |

|              | See page 157.                                                                 | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$008F       | Timer Interrupt Flag Register 2<br>(TFLG2)                                    | Read:<br>Write: | TOF    | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

|              | See page 158.                                                                 | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0090       | Timer Input Capture/Output<br>Compare 0 Register High (TC0H)<br>See page 158. | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9       | Bit 8 |

|              | Gee page 130.                                                                 | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0091       | Timer Input Capture/Output<br>Compare 0 Register Low (TC0L)                   | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|              | See page 158.                                                                 | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0092       | Timer Input Capture/Output<br>Compare 1 Register High (TC1H)                  | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9       | Bit 8 |

|              | See page 159.                                                                 | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0093       | Timer Input Capture/Output<br>Compare 1 Register Low (TC1L)                   | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|              | See page 159.                                                                 | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0094       | Timer Input Capture/Output<br>Compare 2 Register High (TC2H)                  | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9       | Bit 8 |

|              | See page 159.                                                                 | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0095       | Timer Input Capture/Output<br>Compare 2 Register Low (TC2L)                   | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|              | See page 159.                                                                 | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0096       | Timer Input Capture/Output<br>Compare 3 Register High (TC3H)                  | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9       | Bit 8 |

|              | See page 160.                                                                 | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0097       | Timer Input Capture/Output<br>Compare 3 Register Low (TC3L)                   | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|              | See page 160.                                                                 | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| <b>N</b> 1 4 |                                                                               |                 |        | = Unimplen | nented | R      | = Reserved |        | U = Unaffec | ted   |

- Available only on MC68HC912B32 and MC68HC912BC32 devices.

Available only on MC68HC912B32 and MC68HC12BE32 devices.

Available only on MC68HC(9)12BC32 devices.

Figure 2-1. Register Map (Sheet 9 of 19)

**Data Sheet**

| Addr.       | Register Name                                                |                 | Bit 7  | 6          | 5      | 4      | 3          | 2      | 1           | Bit 0 |

|-------------|--------------------------------------------------------------|-----------------|--------|------------|--------|--------|------------|--------|-------------|-------|

| \$0098      | Timer Input Capture/Output<br>Compare 4 Register High (TC4H) | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9       | Bit 8 |

|             | See page 160.                                                | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$0099      | Timer Input Capture/Output<br>Compare 4 Register Low (TC4L)  | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|             | See page 160.                                                | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$009A      | Timer Input Capture/Output<br>Compare 5 Register High (TC5H) | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9       | Bit 8 |

|             | See page 160.                                                | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$009B      | Timer Input Capture/Output<br>Compare 5 Register Low (TC5L)  | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|             | See page 160.                                                | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$009C      | Timer Input Capture/Output<br>Compare 6 Register High (TC6H) | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9       | Bit 8 |

|             | See page 160.                                                | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$009D      | Timer Input Capture/Output<br>Compare 6 Register Low (TC6L)  | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|             | See page 160.                                                | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$009E      | Timer Input Capture/Output<br>Compare 7 Register High (TC7H) | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9       | Bit 8 |

|             | See page 161.                                                | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$009F      | Timer Input Capture/Output<br>Compare 7 Register Low (TC7L)  | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|             | See page 161.                                                | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$00A0      | Pulse Accumulator Control<br>Register (PACTL)                | Read:<br>Write: | 0      | PAEN       | PAMOD  | PEDGE  | CLK1       | CLK0   | PAOVI       | PAI   |

|             | See page 161.                                                | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$00A1      | Pulse Accumulator Flag Register (PAFLG)                      | Read:<br>Write: | 0      | 0          | 0      | 0      | 0          | 0      | PAOVF       | PAIF  |

|             | See page 163.                                                | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$00A2      | Pulse Accumulator Count<br>Register 3 (PACN3)                | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|             | See page 190.                                                | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$00A3      | Pulse Accumulator Count<br>Register 2 (PACN2)                | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|             | See page 190.                                                | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| <b>N.</b> . |                                                              |                 |        | = Unimplen | nented | R      | = Reserved |        | U = Unaffec | ted   |

- Available only on MC68HC912B32 and MC68HC912BC32 devices.

Available only on MC68HC912B32 and MC68HC12BE32 devices.

Available only on MC68HC(9)12BC32 devices.

Figure 2-1. Register Map (Sheet 10 of 19)

| Addr.                  | Register Name                                                 |                 | Bit 7 | 6          | 5      | 4     | 3          | 2     | 1           | Bit 0                |

|------------------------|---------------------------------------------------------------|-----------------|-------|------------|--------|-------|------------|-------|-------------|----------------------|

| \$00A4                 | Pulse Accumulator Count<br>Register 1 (PACN1)                 | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0                |

|                        | See page 190.                                                 | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0                    |

| \$00A5                 | Pulse Accumulator Count<br>Register 0 (PACN0)                 | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0                |

|                        | See page 190.                                                 | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0                    |

| \$00A6                 | 16-Bit Modulus Down-Counter<br>Control Register (MCCTL)       | Read:<br>Write: | MCZI  | MODMC      | RDMCL  | ICLAT | FLMC       | MCEN  | MCPR1       | MCPR0                |

|                        | See page 191.                                                 | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0                    |

| \$00A7                 | 16-Bit Modulus Down-Counter Flag<br>Register (MCFLG)          | Read:<br>Write: | MCZF  | 0          | 0      | 0     | POLF3      | POLF2 | POLF1       | POLF0                |

|                        | See page 192.                                                 | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0                    |

| \$00A8                 | Input Control Pulse Accumulators<br>Control Register (ICPACR) | Read:<br>Write: | 0     | 0          | 0      | 0     | PA3EN      | PA2EN | PA1EN       | PA0EN                |

|                        | See page 193.                                                 | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0                    |

| \$00A9                 | Delay Counter Control Register (DLYCT)                        | Read:<br>Write: | 0     | 0          | 0      | 0     | 0          | 0     | DLY1        | DLY0                 |

|                        | See page 193.                                                 | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0                    |

| \$00AA                 | Input Control Overwrite Register (ICOVW)                      | Read:<br>Write: | NOVW7 | NOVW6      | NOVW5  | NOVW4 | NOVW3      | NOVW2 | NOVW1       | NOVW0                |

|                        | See page 194.                                                 | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0                    |

| \$00AB                 | Input Control System Control<br>Register (ICSYS)              | Read:<br>Write: | SH37  | SH26       | SH15   | HS04  | TFMOD      | PACMX | BUFEN       | LATQ                 |

|                        | See page 194.                                                 | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0                    |

| \$00AC                 | Reserved                                                      | _               | R     | R          | R      | R     | R          | R     | R           | R                    |

| <b>#</b> 00 <b>4 D</b> | Timer Test Register                                           | Read:           | 0     | 0          | 0      | 0     | 0          | 0     | TCBYP       | PCBYP <sup>(1)</sup> |

| \$00AD                 | (TIMTST)<br>See page 196.                                     | Write:          |       |            |        |       |            |       |             |                      |

|                        |                                                               | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0                    |

| \$00AE                 | Timer Port Data Register<br>(PORTT)                           | Read:<br>Write: | PT7   | PT6        | PT5    | PT4   | PT3        | PT2   | PT1         | PT0                  |

|                        | See page 196.                                                 | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0                    |

| \$00AF                 | Data Direction Register for Timer<br>Port (DDRT)              | Read:<br>Write: | DDT7  | DDT6       | DDT5   | DDT4  | DDT3       | DDT2  | DDT1        | DDT0                 |

|                        | See page 197.                                                 | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0                    |

|                        |                                                               |                 |       | = Unimplen | nented | R     | = Reserved |       | U = Unaffec | eted                 |

- 1. Available only on MC68HC912B32 and MC68HC912BC32 devices. 2. Available only on MC68HC912B32 and MC68HC12BE32 devices.

- 3. Available only on MC68HC(9)12BC32 devices.

Figure 2-1. Register Map (Sheet 11 of 19)

| Addr.  | Register Name                                          |                 | Bit 7  | 6          | 5      | 4      | 3          | 2      | 1           | Bit 0 |

|--------|--------------------------------------------------------|-----------------|--------|------------|--------|--------|------------|--------|-------------|-------|

| \$00B0 | 16-Bit Pulse Accumulator B Control<br>Register (PBCTL) | Read:<br>Write: | 0      | PBEN       | 0      | 0      | 0          | 0      | PBOV        | 0     |

|        | See page 197.                                          | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$00B1 | Pulse Accumulator B Flag Register (PBFLG)              | Read:<br>Write: | 0      | 0          | 0      | 0      | 0          | 0      | PBOV        | 0     |

|        | See page 198.                                          | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$00B2 | 8-Bit Pulse Accumulator Holding<br>Register 3 (PA3H)   | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|        | See page 198.                                          | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$00B3 | 8-Bit Pulse Accumulator Holding<br>Register 2 (PA2H)   | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|        | See page 198.                                          | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$00B4 | 8-Bit Pulse Accumulator Holding<br>Register 1 (PA1H)   | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|        | See page 198.                                          | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$00B5 | 8-Bit Pulse Accumulator Holding<br>Register 0 (PA0H)   | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|        | See page 199.                                          | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$00B6 | Modulus Down-Counter Count<br>Register (MCCNT)         | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9       | Bit 8 |

|        | See page 199.                                          | Reset:          | 1      | 1          | 1      | 1      | 1          | 1      | 1           | 1     |

| \$00B7 | Modulus Down-Counter Count<br>Register (MCCNT)         | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|        | See page 199.                                          | Reset:          | 1      | 1          | 1      | 1      | 1          | 1      | 1           | 1     |

| \$00B8 | Timer Input Capture Holding<br>Register 0 (TC0H)       | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9       | Bit 8 |

|        | See page 200.                                          | Reset:          | 0      | 0          | 1      | 0      | 0          | 0      | 0           | 0     |

| \$00B9 | Timer Input Capture Holding<br>Register 0 (TC0H)       | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|        | See page 200.                                          | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$00BA | Timer Input Capture Holding<br>Register 1 (TC1H)       | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9       | Bit 8 |

|        | See page 200.                                          | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

| \$00BB | Timer Input Capture Holding<br>Register 1 (TC1H)       | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1       | Bit 0 |

|        | See page 200.                                          | Reset:          | 0      | 0          | 0      | 0      | 0          | 0      | 0           | 0     |

|        |                                                        |                 |        | = Unimplen | nented | R      | = Reserved |        | U = Unaffec | ted   |

- Available only on MC68HC912B32 and MC68HC912BC32 devices.

Available only on MC68HC912B32 and MC68HC12BE32 devices.

Available only on MC68HC(9)12BC32 devices.

Figure 2-1. Register Map (Sheet 12 of 19)

| Addr.  | Register Name                                                      |                 | Bit 7  | 6          | 5      | 4      | 3                  | 2      | 1           | Bit 0 |

|--------|--------------------------------------------------------------------|-----------------|--------|------------|--------|--------|--------------------|--------|-------------|-------|

| \$00BC | Timer Input Capture Holding<br>Register 2 (TC2H)                   | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11             | Bit 10 | Bit 9       | Bit 8 |

|        | See page 201.                                                      | Reset:          | 0      | 0          | 0      | 0      | 0                  | 0      | 0           | 0     |

| \$00BD | Timer Input Capture Holding<br>Register 2 (TC2H)<br>See page 201.  | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3              | Bit 2  | Bit 1       | Bit 0 |

|        |                                                                    | Reset:          | 0      | 0          | 0      | 0      | 0                  | 0      | 0           | 0     |

| \$00BE | Timer Input Capture Holding<br>Register 3 (TC3H)                   | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11             | Bit 10 | Bit 9       | Bit 8 |

|        | See page 201.                                                      | Reset:          | 0      | 0          | 0      | 0      | 0                  | 0      | 0           | 0     |

| \$00BF | Timer Input Capture Holding<br>Register 3 (TC3H)                   | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3              | Bit 2  | Bit 1       | Bit 0 |

|        | See page 201.                                                      | Reset:          | 0      | 0          | 0      | 0      | 0                  | 0      | 0           | 0     |

| \$00C0 | SCI 0 Baud Rate Control Register<br>High (SC0BDH)<br>See page 206. | Read:<br>Write: | BTST   | BSPL       | BRLD   | SBR12  | SBR11              | SBR10  | SBR9        | SBR8  |

|        |                                                                    | Reset:          | 0      | 0          | 0      | 0      | 0                  | 0      | 0           | 0     |

| \$00C1 | SCI 0 Baud Rate Control Register<br>Low (SC0BDL)                   | Read:<br>Write: | SBR7   | SBR6       | SBR5   | SBR4   | SBR3               | SBR2   | SBR1        | SBR0  |

|        | See page 206.                                                      | Reset:          | 0      | 0          | 0      | 0      | 0                  | 1      | 0           | 0     |

| \$00C2 | SCI Control Register 1<br>(SC0CR1)                                 | Read:<br>Write: | LOOPS  | WOMS       | RSRC   | М      | WAKE               | ILT    | PE          | PT    |

|        | See page 207.                                                      | Reset:          | 0      | 0          | 0      | 0      | 0                  | 0      | 0           | 0     |

| \$00C3 | SCI Control Register 2<br>(SC0CR2)                                 | Read:<br>Write: | TIE    | TCIE       | RIE    | ILIE   | TE                 | RE     | RWU         | SBK   |

|        | See page 209.                                                      | Reset:          | 0      | 0          | 0      | 0      | 0                  | 0      | 0           | 0     |

|        | SCI Status Register 1<br>(SC0SR1)                                  | Read:           | TDRE   | TC         | RDRF   | IDLE   | OR                 | NF     | FE          | PF    |

| \$00C4 |                                                                    | Write:          |        |            |        |        |                    |        |             |       |

|        | See page 210.                                                      | Reset:          | 1      | 1          | 0      | 0      | 0                  | 0      | 0           | 0     |

|        | SCI Status Register 2                                              | Read:           | 0      | 0          | 0      | 0      | 0                  | 0      | 0           | RAF   |

| \$00C5 | (SCOSR2)                                                           | Write:          |        |            |        |        |                    |        |             |       |

|        | See page 212.                                                      | Reset:          | 0      | 0          | 0      | 0      | 0                  | 0      | 0           | 0     |

| \$00C6 | SCI Data Register High<br>(SCODRH)                                 | Read:<br>Write: | R8     | Т8         | 0      | 0      | 0                  | 0      | 0           | 0     |

|        | See page 213.                                                      | Reset:          | U      | U          | 0      | 0      | 0                  | 0      | 0           | 0     |

| \$00C7 | SCI Data Register Low<br>(SC0DRL)                                  | Read:<br>Write: | R7T7   | R6T6       | R5T5   | R4T4   | R3T3<br>d by reset | R2T2   | R1T1        | R0T0  |

|        | See page 213.                                                      | Reset:          |        | 1          |        |        |                    |        |             |       |

| Notes: |                                                                    |                 |        | = Unimplen | nented | R      | = Reserved         |        | U = Unaffec | ted   |

**Data Sheet**

- 1. Available only on MC68HC912B32 and MC68HC912BC32 devices.

- 2. Available only on MC68HC912B32 and MC68HC12BE32 devices.

3. Available only on MC68HC(9)12BC32 devices.

Figure 2-1. Register Map (Sheet 13 of 19)

- 1. Available only on MC68HC912B32 and MC68HC912BC32 devices.

- 2. Available only on MC68HC912B32 and MC68HC12BE32 devices.

- 3. Available only on MC68HC(9)12BC32 devices.

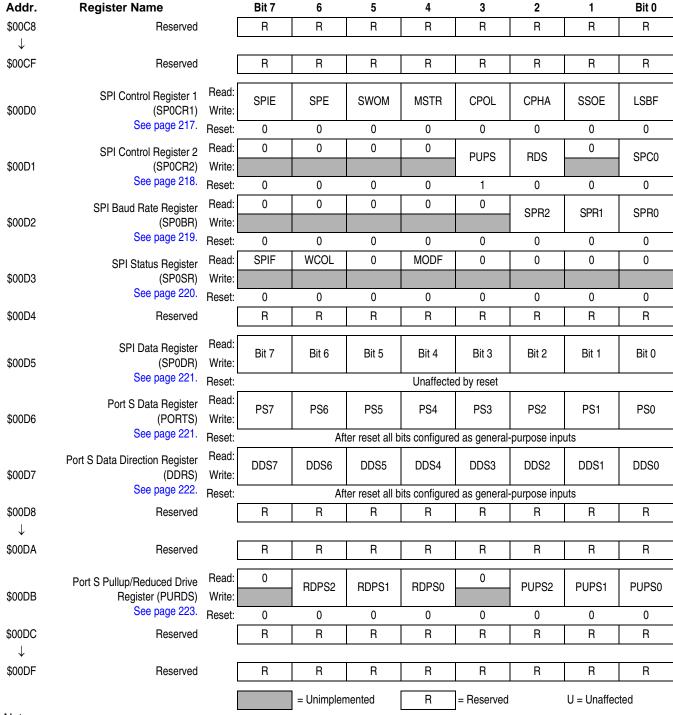

Figure 2-1. Register Map (Sheet 14 of 19)

M68HC12B Family — Rev. 8.0

| Addr.       | Register Name                                                  |                 | Bit 7 | 6          | 5      | 4       | 3          | 2       | 1           | Bit 0   |

|-------------|----------------------------------------------------------------|-----------------|-------|------------|--------|---------|------------|---------|-------------|---------|

|             | Slow Mode Divider Register                                     | Read:           | 0     | 0          | 0      | 0       | 0          | SLDV2   | SLDV1       | SLDV0   |

| \$00E0      | (SLOW)<br>See page 123.                                        | Write:          |       |            |        |         |            | OLDVL   | OLDVI       | OLDVO   |

|             | 200 page 1201                                                  | Reset:          | 0     | 0          | 0      | 0       | 0          | 0       | 0           | 0       |

| \$00E1      | Reserved                                                       |                 | R     | R          | R      | R       | R          | R       | R           | R       |

| ↓<br>•••=== | 5                                                              | ſ               |       |            |        |         |            |         |             |         |

| \$00EF      | Reserved                                                       |                 | R     | R          | R      | R       | R          | R       | R           | R       |

| \$00F0      | EEPROM Configuration Register (EEMCR)                          | Read:<br>Write: | 1     | 1          | 1      | 1       | 1          | EESWAI  | PROTLCK     | EERC    |

|             | See page 99.                                                   | Reset:          | 1     | 1          | 1      | 1       | 1          | 1       | 0           | 0       |

| \$00F1      | EEPROM Block Protect Register (EEPROT)                         | Read:<br>Write: | 1     | 1          | 1      | BRPROT4 | BRPROT3    | BRPROT2 | BRPROT1     | BRPROT0 |

|             | See page 100.                                                  | Reset:          | 1     | 1          | 1      | 1       | 1          | 1       | 1           | 1       |

| \$00F2      | EEPROM Test Register (EETST) See page 101.                     | Read:<br>Write: | EEODD | EEVEN      | MARG   | EECPD   | EECPRD     | 0       | EECPM       | 0       |

|             | See page 101.                                                  | Reset:          | 0     | 0          | 0      | 0       | 0          | 0       | 0           | 0       |

| \$00F3      | EEPROM Control Register (EEPROG)                               | Read:<br>Write: | BULKP | 0          | 0      | ВҮТЕ    | ROW        | ERASE   | EELAT       | EEPGM   |

|             | See page 102.                                                  | Reset:          | 1     | 0          | 0      | 0       | 0          | 0       | 0           | 0       |

| \$00F4      | FLASH EEPROM Lock Control<br>Register (FEELCK) <sup>(1)</sup>  | Read:<br>Write: | 0     | 0          | 0      | 0       | 0          | 0       | 0           | LOCK    |

|             | See page 106.                                                  | Reset:          | 0     | 0          | 0      | 0       | 0          | 0       | 0           | 0       |

| \$00F5      | FLASH EEPROM Configuration<br>Register (FEEMCR) <sup>(1)</sup> | Read:<br>Write: | 0     | 0          | 0      | 0       | 0          | 0       | 0           | ВООТР   |

|             | See page 106.                                                  | Reset:          | 0     | 0          | 0      | 0       | 0          | 0       | 0           | 1       |

| \$00F6      | FLASH EEPROM Test<br>Register (FEETST) <sup>(1)</sup>          | Read:<br>Write: | FSTE  | GADR       | HVT    | FENLV   | FDISVFP    | VTCK    | STRE        | MWPR    |

|             | See page 107.                                                  | Reset:          | 0     | 0          | 0      | 0       | 0          | 0       | 0           | 0       |

| \$00F7      | FLASH EEPROM Control Register (FEECTL) <sup>(1)</sup>          | Read:<br>Write: | 0     | 0          | 0      | FEESWAI | SVFP       | ERAS    | LAT         | ENPE    |

|             | See page 108.                                                  | Reset:          | 0     | 0          | 0      | 0       | 0          | 0       | 0           | 0       |

| \$00F8      | BDLC Control Register 1 (BCR1) <sup>(2)</sup>                  | Read:<br>Write: | IMSG  | CLKS       | R1     | R0      | 0<br>R     | 0<br>R  | ΙE          | WCM     |

|             | See page 249.                                                  | Reset:          | 1     | 1          | 1      | 0       | 0          | 0       | 0           | 0       |

| \$00F9      | BDLC State Vector Register (BSVR) <sup>(2)</sup>               | Read:<br>Write: | 0     | 0          | 13     | 12      | I1         | 10      | 0           | 0       |

|             | See page 256.                                                  | Reset:          | 0     | 0          | 0      | 0       | 0          | 0       | 0           | 0       |

|             |                                                                |                 |       | = Unimplen | nented | R       | = Reserved |         | U = Unaffec | ted     |

**Data Sheet**

- 1. Available only on MC68HC912B32 and MC68HC912BC32 devices.

- 2. Available only on MC68HC912B32 and MC68HC12BE32 devices.

- 3. Available only on MC68HC(9)12BC32 devices.

Figure 2-1. Register Map (Sheet 15 of 19)

| Addr.  | Register Name                                                        |                 | Bit 7 | 6          | 5      | 4            | 3              | 2      | 1           | Bit 0  |

|--------|----------------------------------------------------------------------|-----------------|-------|------------|--------|--------------|----------------|--------|-------------|--------|

| \$00FA | BDLC Control Register 2 (BCR2) <sup>(2)</sup>                        | Read:<br>Write: | ALOOP | DLOOP      | RX4XE  | NBFS         | TEOD           | TSIFR  | TMIFR1      | TMIFR0 |

|        | See page 250.                                                        | Reset:          | 1     | 1          | 0      | 0            | 0              | 0      | 0           | 0      |

| \$00FB | BDLC Data Register (BDR) <sup>(2)</sup>                              | Read:<br>Write: | BD7   | BD6        | BD5    | BD4          | BD3            | BD2    | BD1         | BD0    |

|        | See page 258.                                                        | Reset:          |       |            |        | Indeterminat | te after reset |        |             |        |

| \$00FC | BDLC Analog Roundtrip Delay<br>Register (BARD) <sup>(2)</sup>        | Read:<br>Write: | ATE   | RXPOL      | 0      | 0            | BO3            | BO2    | BO1         | B00    |

|        | See page 259.                                                        | Reset:          | 1     | 1          | 0      | 0            | 0              | 1      | 1           | 1      |

| \$00FD | Port DLC Control Register (DLCSCR) <sup>(2)</sup>                    | Read:<br>Write: | 0     | 0          | 0      | 0            | 0              | BDLCEN | PUPDLC      | RDPDLC |

|        | See page 260.                                                        | Reset:          | 0     | 0          | 0      | 0            | 0              | 0      | 0           | 0      |

| \$00FE | Port DLC Data Register<br>(PORTDLC) <sup>(2)</sup>                   | Read:<br>Write: | 0     | Bit 6      | Bit 5  | Bit 4        | Bit 3          | Bit 2  | Bit 1       | Bit 0  |

|        | See page 261.                                                        | Reset:          | 0     | U          | U      | U            | U              | U      | U           | U      |

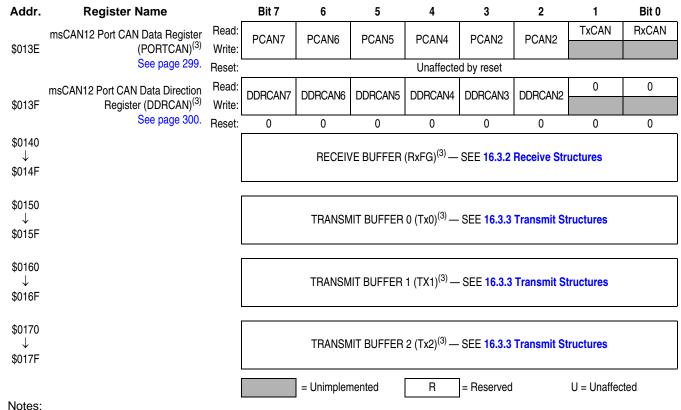

| \$00FF | Port DLC Data Direction Register (DDRDLC) <sup>(2)</sup>             | Read:<br>Write: | 0     | DDDLC6     | DDDLC5 | DDDLC4       | DDDLC3         | DDDLC2 | DDDLC1      | DDDLC0 |